# IPC-A-600G

Acceptability of Printed Boards

IPC-A-600G

July 2004

A standard developed by IPC

Supersedes IPC-A-600F November 1999

2215 Sanders Road, Northbrook, IL 60062-6135 Tel. 847.509.9700 Fax 847.509.9798 www.ipc.org

| The Principles of<br>Standardization                             | In May 1995 the IPC's Technical Activities Executive Commi<br>Standardization as a guiding principle of IPC's standardization                                                                                                                                                                                                                                                                                                                                                                                                            | · ·                                                                                                                                                                                                                                                              |

|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                  | <ul> <li>Standards Should:</li> <li>Show relationship to Design for Manufacturability<br/>(DFM) and Design for the Environment (DFE)</li> <li>Minimize time to market</li> <li>Contain simple (simplified) language</li> <li>Just include spec information</li> <li>Focus on end product performance</li> <li>Include a feedback system on use and<br/>problems for future improvement</li> </ul>                                                                                                                                        | <ul> <li>Standards Should Not:</li> <li>Inhibit innovation</li> <li>Increase time-to-market</li> <li>Keep people out</li> <li>Increase cycle time</li> <li>Tell you how to make something</li> <li>Contain anything that cannot be defended with data</li> </ul> |

| Notice                                                           | IPC Standards and Publications are designed to serve the public<br>understandings between manufacturers and purchasers, facilitate<br>ment of products, and assisting the purchaser in selecting and<br>proper product for his particular need. Existence of such Standards<br>any respect preclude any member or nonmember of IPC from<br>not conforming to such Standards and Publication, nor shall the<br>Publications preclude their voluntary use by those other than the<br>is to be used either domestically or internationally. | ating interchangeability and improve-<br>obtaining with minimum delay the<br>dards and Publications shall not in<br>manufacturing or selling products<br>he existence of such Standards and                                                                      |

|                                                                  | Recommended Standards and Publications are adopted by IPC<br>tion may involve patents on articles, materials, or processes. If<br>any liability to any patent owner, nor do they assume any obli-<br>the Recommended Standard or Publication. Users are also whiselves against all claims of liabilities for patent infringement.                                                                                                                                                                                                        | By such action, IPC does not assume igation whatever to parties adopting                                                                                                                                                                                         |

| IPC Position<br>Statement on<br>Specification<br>Revision Change | It is the position of IPC's Technical Activities Executive Com<br>implementation of IPC publications is voluntary and is part of<br>customer and supplier. When an IPC publication is updated at<br>is the opinion of the TAEC that the use of the new revision at<br>is not automatic unless required by the contract. The TAEC re-<br>revision.                                                                                                                                                                                        | f a relationship entered into by<br>nd a new revision is published, it<br>s part of an existing relationship                                                                                                                                                     |

| Why is there<br>a charge for<br>this document?                   | Your purchase of this document contributes to the ongoing de<br>try standards and publications. Standards allow manufacturers<br>stand one another better. Standards allow manufacturers greate<br>up their processes to meet industry standards, allowing them t                                                                                                                                                                                                                                                                        | , customers, and suppliers to under-<br>er efficiencies when they can set                                                                                                                                                                                        |

|                                                                  | IPC spends hundreds of thousands of dollars annually to supp<br>and publications development process. There are many rounds<br>the committees spend hundreds of hours in review and develo<br>ticipates in committee activities, typesets and circulates docum<br>procedures to qualify for ANSI approval.                                                                                                                                                                                                                               | s of drafts sent out for review and opment. IPC's staff attends and par-                                                                                                                                                                                         |

|                                                                  | IPC's membership dues have been kept low to allow as many<br>Therefore, the standards and publications revenue is necessary<br>price schedule offers a 50% discount to IPC members. If your<br>publications, why not take advantage of this and the many off<br>well? For more information on membership in IPC, please vis                                                                                                                                                                                                              | y to complement dues revenue. The<br>r company buys IPC standards and<br>her benefits of IPC membership as                                                                                                                                                       |

|                                                                  | Thank you for your continued support.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                  |

IPC-A-600G

# Acceptability of Printed Boards

Developed by the IPC-A-600 Task Group (7-31a) of the Product Assurance Committee (7-30) of IPC

Supersedes:

IPC-A-600F - November 1999

Users of this publication are encouraged to participate in the development of future revisions.

Contact:

IPC 2215 Sanders Road Northbrook, Illinois 60062-6135 Tel 847 509.9700 Fax 847 509.9798

# Acknowledgement

Any standard involving a complex technology draws material from a vast number of sources. While the principal members of the A-600 Task Group (7-31a) of the Product Assurance Committee (7-30) are shown below, it is not possible to include all of those who assisted in the evolution of this standard. To each of them, the members of IPC extend their gratitude. who assisted in the evolution of this standard. To each of them, the members of IPC extend their gratitude. Special thanks goes to the members of the D-30 Rigid Printed Board Committee for their efforts in establishing acceptance criteria for printed boards.

Product Assurance Committee Chair Mel Parrish Soldering Technology International

Technical Liaisons of the IPC Board of Directors

Peter Bigelow IMI Inc.

Sammy Yi Flextronics International

- Mary E. Bellon, Boeing Satellite Systems Gerald Leslie Bogert, Bechtel Plant Machinery, Inc.

- Scott A. Bowles, Sovereign Circuits Inc. Ronald J. Brock, NSWC - Crane

- RUIIAIU J. BIOCK, NSWC CIAIIE

- Dennis J. Cantwell, Printed Circuits Inc.

- Byron Case, L-3 Communications

- Pei-Liang Chen, Shanghai Printronics Circuit

- Phillip Chen, Northrop Grumman Canada Corporation

- Christine R. Coapman, Delphi Delco Electronics Systems

- W. Glenn Colescott, Delphi Delco Electronics Systems

- Dan Colvin, Tyco PCG/Logan Division

- Christopher Conklin, Lockheed Martin Corporation

- David J. Corbett, Defense Supply Center Columbus

Dennis DeBord, Nortel Networks Center 1

- C. Don Dupriest, Lockheed Martin Missiles & Fire Control

- Theodore Edwards, Dynaco Corp.

- Werner Engelmaier, Engelmaier Associates, L.C.

- Gary M. Ferrari, C.I.D.+, Ferrari Technical Services

- Lionel Fullwood, WKK Distribution Ltd.

- Mahendra S. Gandhi, Northrop Grumman Thomas F. Gardeski, E. I. du Pont de

- Nemours and Co. Floyd L. Gentry, Sandia National Labs Albuquerque

- Constantino J. Gonzalez, ACME Training & Consulting

IPC-A-600 Task Group Chair Mark Buechner BAE Systems IPC Rigid Printed Board Committee Chair C. Don Dupriest Lockheed Martin Missiles & Fire Control

Robert J. Gordon, Visteon Corp. Hue T. Green. Lockheed Martin Space Systems Company Ken Greene, Siemens Energy and Automation Michael R. Green, Lockheed Martin Space Systems Company Samy Hanna, AT&S Austria Technologie & Systemtechnik Michael E. Hill, Colonial Circuits Phillip E. Hinton, Hinton 'PWB' Engineering Kazuo Hirasaka, Eastern Manufacturing Ted J. Jones, NSWC - Crane Thomas E. Kemp, Rockwell Collins Arshad Khan, Celestica International Inc. Clarence W. Knapp, Litton Systems Inc. Jason Koch, Robisan Laboratory Inc. Raymond L. Kolonchuk, Jr., Defense Supply Center Columbus Nick Koop, Minco Products Inc. Leo P. Lambert, EPTAC Corporation Michael G. Luke, C.I.D., Raytheon Company Chris Mahanna, Robisan Laboratory Inc. Wesley R. Malewicz, Draeger Medical Systems, Inc. Susan S. Mansilla, Robisan Laboratory Inc. Rene R. Martinez, Northrop Grumman Brian C. McCrory, Delsen Testing Laboratories Ronald McIlnay, Medtronic Physio-Control Randy McNutt, Northrop Grumman Renee J. Michalkiewicz, Trace Laboratories

James H. Moffitt, Moffitt Consulting Services Bob Neves, Microtek Laboratories Benny Nilsson, Ericsson AB Debora L. Obitz, Trace Laboratories - East William Ortloff, B/C Engineering Donald G. Pucci, Gould Electronics Inc. Jim R. Reed, Dell Computer Corporation Randy R. Reed, Merix Corporation Gary C. Roper, Eagle Circuits Inc. Visa Ruuhonen, Nokia Networks Russell S. Shepherd, Microtek Laboratories Lowell Sherman, Defense Supply Center Columbus Akikazu Shibata, Ph.D., JPCA-Japan Printed Circuit Association Hans L. Shin, Pacific Testing Laboratories, Inc. Frank A. Stetson, Training & Certification Specialists Roger Su, L-3 Communications Gail Tennant, Celestica Ronald E. Thompson, NSWC - Crane Dung Q. Tiet, Lockheed Martin Space Systems Company Robert Vanech Rob Walls, C.I.D.+, PIEK International Education Centre BV Ronnie Walker, Northrop Grumman Clark F. Webster, ALL Flex Inc. Robert B. Whitehouse, Sanmina-SCI Corporation Philip W. Wittmer, Delphi Delco Electronics Systems

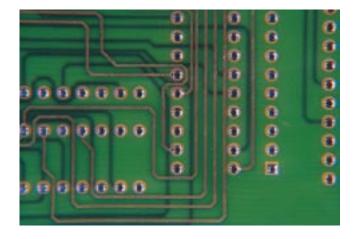

PWB on front and back cover photo courtesy of U.S. Robotics

- Fast

# Table of Contents

| Ack | nowledge           | ement                                              | i    |

|-----|--------------------|----------------------------------------------------|------|

| 1.0 | Introduc           | ction                                              | 1    |

| 1.1 | Scope .            |                                                    | 1    |

| 1.2 | Purpose            | •                                                  | 1    |

| 1.3 | Approa             | ch To This Document                                | 1    |

| 1.4 | Classifi           | cation                                             | 1    |

| 1.5 | Accepta            | ince Criteria                                      | 2    |

| 1.6 | Applica            | ble Documents                                      | 3    |

| 1.7 | Dimens             | ions And Tolerances                                | 3    |

| 1.8 | Terms A            | And Definitions                                    | 3    |

| 1.9 | Workma             | anship                                             | 3    |

| 2.0 | Externa            | Ily Observable Characteristics                     | 4    |

| 2.1 | Board E            | dges                                               | 4    |

|     | 2.1.1              | Burrs                                              |      |

|     | 2.1.1.1<br>2.1.1.2 | Nonmetallic Burrs                                  |      |

|     | 2.1.1.2            | Nicks                                              |      |

|     | 2.1.3              | Haloing                                            |      |

| 2.2 | Base Ma            | aterial                                            | 9    |

|     | 2.2.1              | Weave Exposure                                     | . 10 |

|     | 2.2.2              | Weave Texture                                      |      |

|     | 2.2.3<br>2.2.4     | Exposed/Disrupted Fibers<br>Pits and Voids         |      |

| 2.3 | Base Ma            | aterial Subsurface                                 | . 14 |

|     | 2.3.1              | Measling                                           | . 17 |

|     | 2.3.2              | Crazing                                            |      |

|     | 2.3.3<br>2.3.4     | Delamination/Blister<br>Foreign Inclusions         |      |

| 2.4 |                    | Coatings and Fused Tin Lead                        |      |

| 2.4 | 2.4.1              | Nonwetting                                         |      |

|     | 2.4.2              | Dewetting                                          |      |

| 2.5 | Holes –            | Plated-Through – General                           | . 23 |

|     | 2.5.1              | Nodules/Burrs                                      | . 23 |

|     | 2.5.2              | Pink Ring                                          |      |

|     | 2.5.3<br>2.5.4     | Voids - Copper Plating<br>Voids - Finished Coating |      |

|     | 2.5.4<br>2.5.5     | Lifted Lands - (Visual)                            |      |

| 2.6 |                    | Unsupported                                        |      |

|     | 2.6.1              | Haloing                                            |      |

| 2.7  | Printed   | <b>Contacts</b>                                   |

|------|-----------|---------------------------------------------------|

|      | 2.7.1     | Surface Plating - General                         |

|      | 2.7.1.1   | Surface Plating - Wire Bond Pads 30               |

|      | 2.7.2     | Burrs on Edge-Board Contacts 31                   |

|      | 2.7.3     | Adhesion of Overplate 32                          |

| 2.8  | Marking   |                                                   |

|      | 2.8.1     | Etched Marking                                    |

|      | 2.8.2     | Screened or Ink Stamped                           |

|      |           | Marking                                           |

| 2.9  | Solder F  | Resist (Solder Mask)                              |

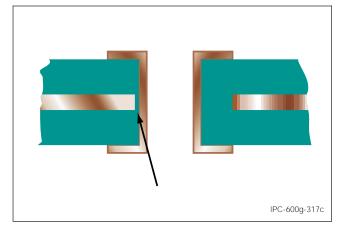

|      | 2.9.1     | Coverage Over Conductors                          |

|      |           | (Skip Coverage) 37                                |

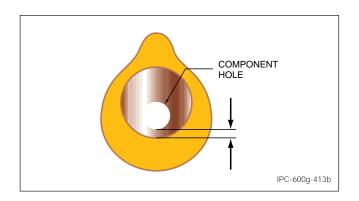

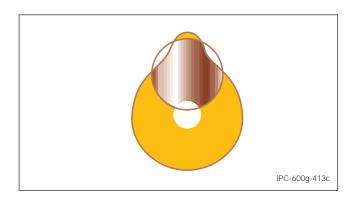

|      | 2.9.2     | Registration to Holes (All Finishes) 38           |

|      | 2.9.3     | Registration to Other Conductive                  |

|      | 0 0 0 1   | Patterns                                          |

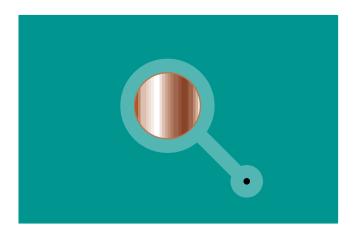

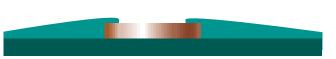

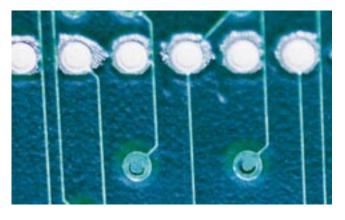

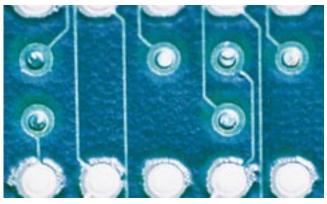

|      | 2.9.3.1   | Ball Grid Array (Solder Resist-<br>Defined Lands) |

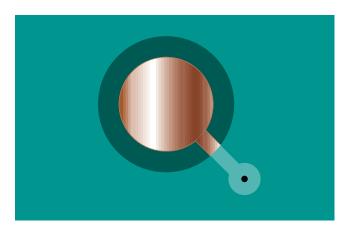

|      | 2.9.3.2   | Ball Grid Array (Copper-Defined                   |

|      | 2.7.0.2   | Lands)                                            |

|      | 2.9.3.3   | Ball Grid Array (Solder Dam) 42                   |

|      | 2.9.4     | Blisters/Delamination                             |

|      | 2.9.5     | Adhesion (Flaking or Peeling)                     |

|      | 2.9.6     | Waves/Wrinkles/Ripples                            |

|      | 2.9.7     | Tenting (Via Holes) 46                            |

|      | 2.9.8     | Soda Strawing 47                                  |

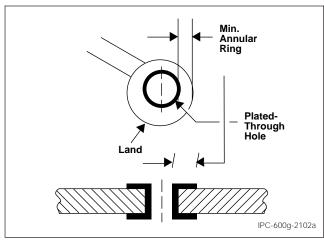

| 2.10 | Pattern   | Definition - Dimensional 48                       |

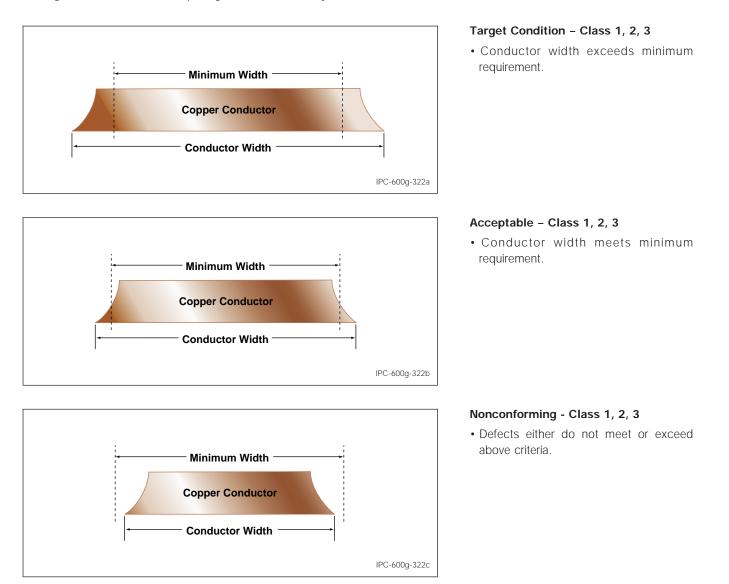

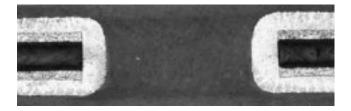

|      | 2.10.1    | Conductor Width and Spacing 48                    |

|      |           | Conductor Width 49                                |

|      |           | Conductor Spacing 50                              |

|      | 2.10.2    | External Annular Ring -                           |

|      | 2.10.3    | Measurement 51<br>External Annular Ring -         |

|      | 2.10.5    | Supported Holes                                   |

|      | 2.10.4    | External Annular Ring -                           |

|      |           | Unsupported Holes 53                              |

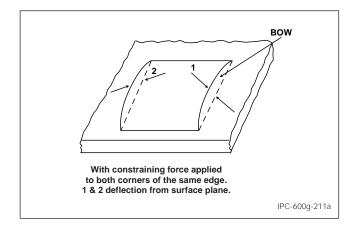

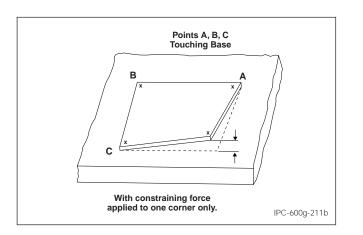

| 2.11 | Flatness  | <b>5</b> 54                                       |

| 3.0  | Internall | y Observable Characteristics 55                   |

| 3.1  | Dielectri | c Materials                                       |

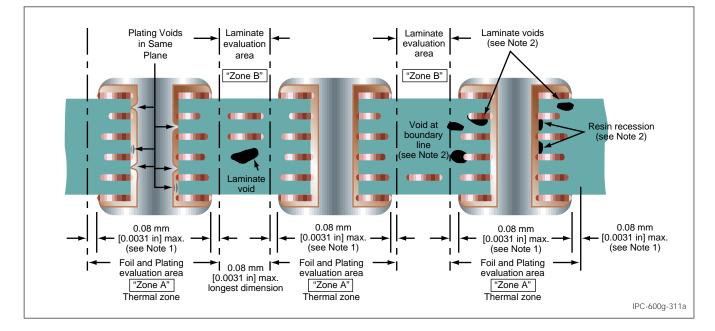

| •••• | 3.1.1     | Laminate Voids (Outside Thermal                   |

|      | 0.1.1     | Zone)                                             |

|      | 3.1.2     | Registration/Conductors to Holes 58               |

|      | 3.1.3     | Clearance Hole, Unsupported,                      |

|      |           | to Power/Ground Planes 59                         |

|      | 3.1.4     | Delamination/Blister 60                           |

|      | 3.1.5     | Etchback 61                                       |

# Table of Contents

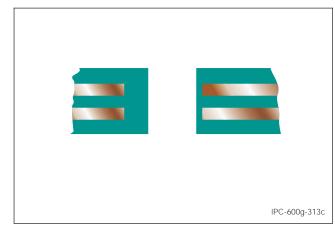

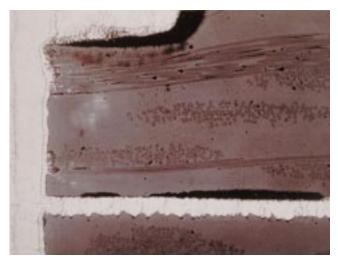

|     | 3.1.5.1  | Etchback                                                 | 62 |

|-----|----------|----------------------------------------------------------|----|

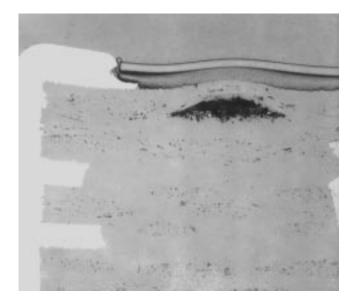

|     | 3.1.5.2  | Negative Etchback                                        | 63 |

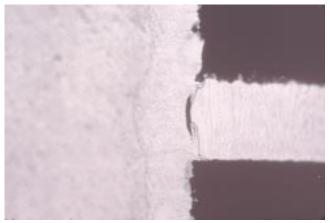

|     | 3.1.6    | Smear Removal                                            | 64 |

|     | 3.1.7    | Dielectric Material, Clearance,                          |    |

|     |          | Metal Plane for Supported Holes                          |    |

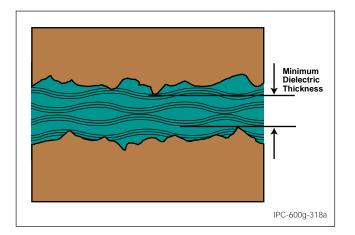

|     | 3.1.8    | Layer-to-Layer Spacing                                   |    |

|     | 3.1.9    | Resin Recession                                          | 67 |

| 3.2 | Conduct  | tive Patterns - General                                  | 68 |

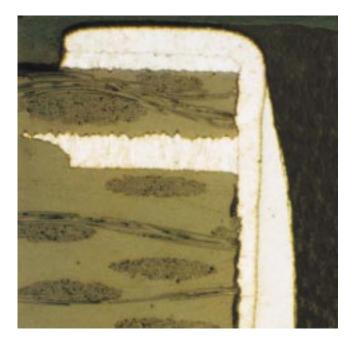

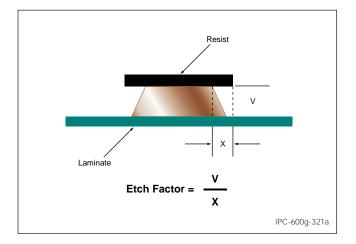

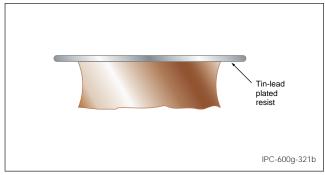

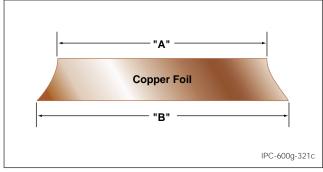

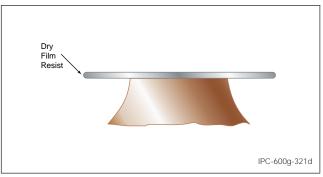

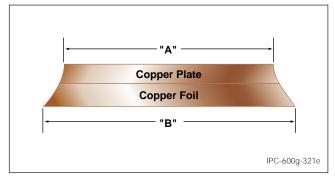

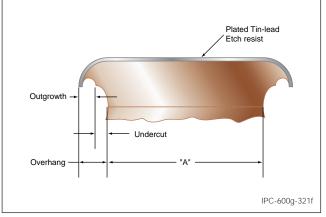

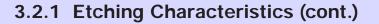

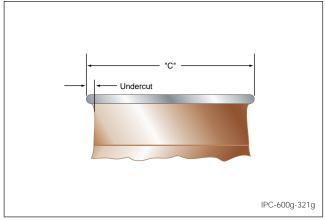

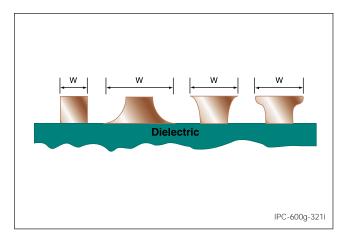

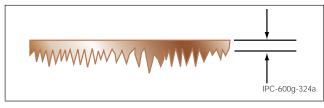

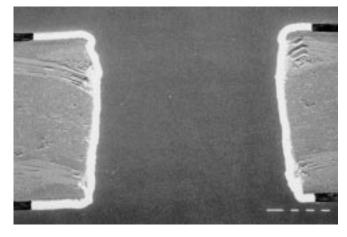

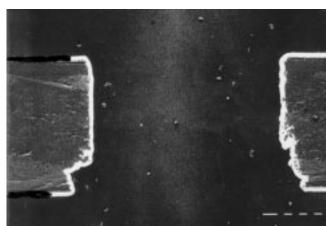

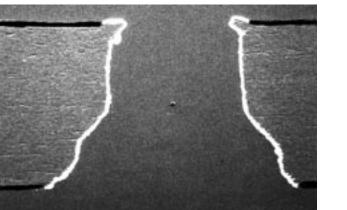

|     | 3.2.1    | Etching Characteristics                                  | 69 |

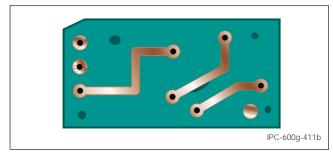

|     | 3.2.2    | Print and Etch                                           | 71 |

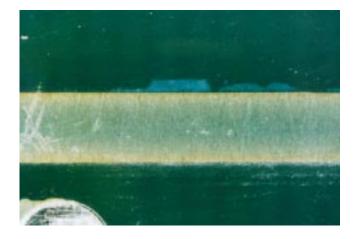

|     | 3.2.3    | Surface Conductor Thickness                              |    |

|     |          | (Foil Plus Plating)                                      |    |

|     | 3.2.4    | Foil Thickness - Internal Layers                         | 72 |

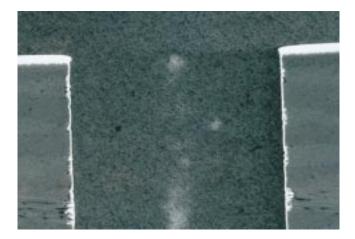

| 3.3 | Plated-T | hrough Holes - General                                   | 73 |

|     | 3.3.1    | Annular Ring - Internal Layers                           |    |

|     | 3.3.2    | Lifted Lands - (Cross-Sections)                          | 77 |

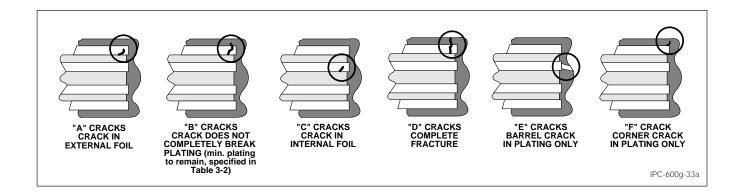

|     | 3.3.3    | Foil Crack - (Internal Foil)                             | 70 |

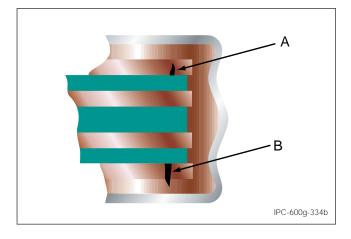

|     | 2.2.4    | "C" Crack                                                |    |

|     | 3.3.4    | Foil Crack - (External Foil)                             | 79 |

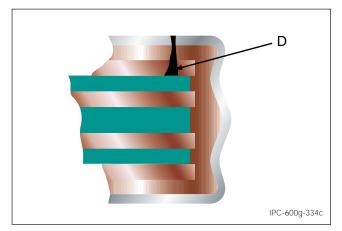

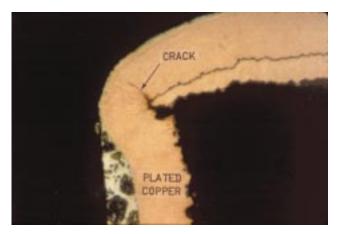

|     | 3.3.5    | Plating Crack - (Barrel)<br>"E" Crack                    | 80 |

|     | 3.3.6    | Plating Crack - (Corner)<br>"F" Crack                    | 81 |

|     | 3.3.7    | Plating Nodules                                          | 82 |

|     | 3.3.8    | Copper Plating Thickness -                               |    |

|     |          | Hole Wall                                                | 83 |

|     | 3.3.9    | Plating Voids                                            | 84 |

|     | 3.3.10   | Solder Coating Thickness                                 |    |

|     |          | (Only When Specified)                                    |    |

|     | 3.3.11   | Solder Resist Thickness                                  |    |

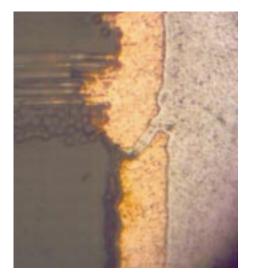

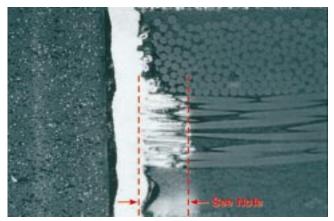

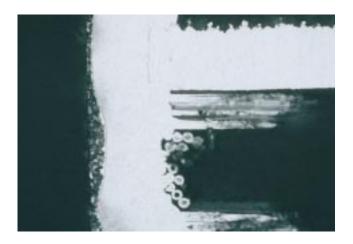

|     | 3.3.12   | Wicking                                                  |    |

|     | 3.3.12.1 | Wicking, Clearance Holes                                 | 88 |

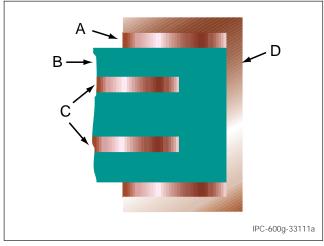

|     | 3.3.13   | Innerlayer Separation - Vertical<br>(Axial) Microsection | 00 |

|     | 3.3.14   | Innerlayer Separation - Horizontal                       | 07 |

|     | 5.5.14   | (Transverse) Microsection                                | 90 |

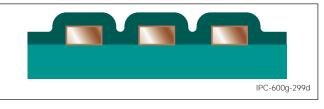

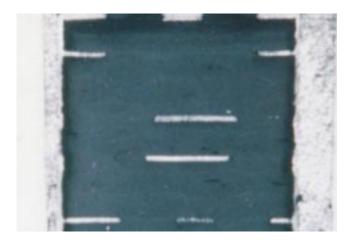

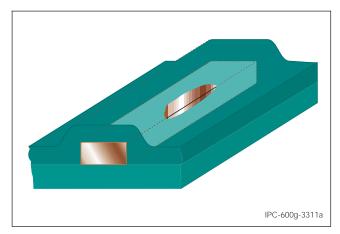

|     | 3.3.15   | Material Fill of Blind and Buried                        | /0 |

|     | 010110   | Vias                                                     | 91 |

| 3.4 | Plated-T | hrough Holes - Drilled                                   | 92 |

|     | 3.4.1    | Burrs                                                    |    |

|     | 3.4.2    | Nailheading                                              |    |

| 3.5 | Plated-T | hrough Holes - Punched                                   | 95 |

|     | 3.5.1    | Roughness and Nodules                                    |    |

|     | 3.5.2    | Flare                                                    |    |

|     |          |                                                          | 00 |

| 4.0 | Miscella | neous                                                    | 98 |

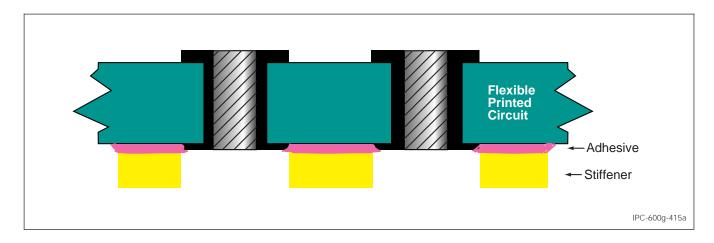

| 4.1  | Flexible  | And Rigid-Flex Printed Wiring 98                              |

|------|-----------|---------------------------------------------------------------|

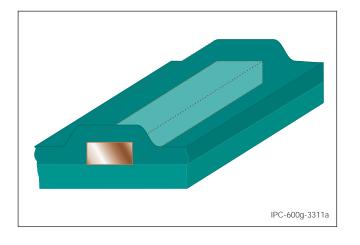

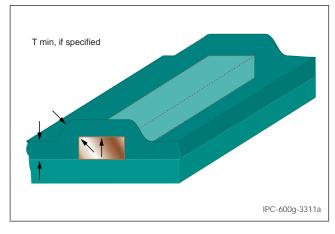

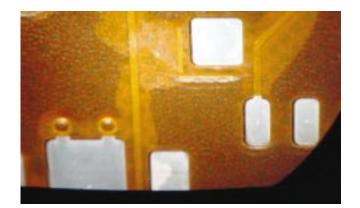

|      | 4.1.1     | Coverlayer Coverage - Coverfilm<br>Separations                |

|      | 4.1.2     | Coverlayer/Cover Coat Coverage<br>Adhesives                   |

|      | 4.1.2.1   | Adhesive Squeeze-Out -<br>Land Area                           |

|      | 4.1.2.2   | Adhesive Squeeze-Out -<br>Foil Surface                        |

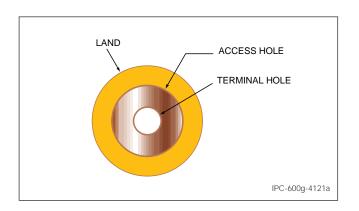

|      | 4.1.3     | Access Hole Registration for<br>Coverlayer and Stiffeners 102 |

|      | 4.1.4     | Plating Defects 103                                           |

|      | 4.1.5     | Stiffener Bonding 104                                         |

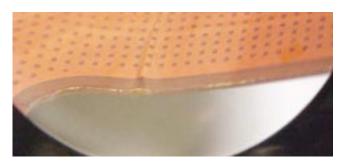

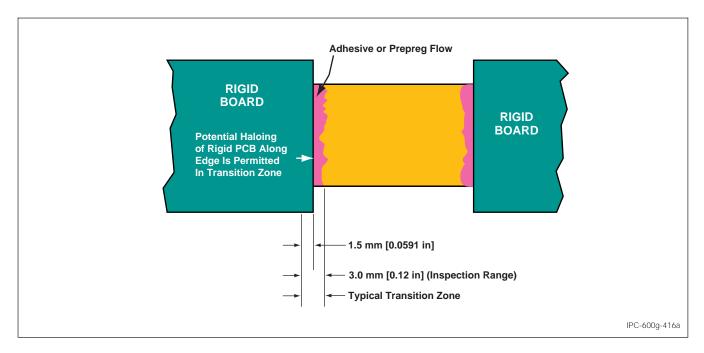

|      | 4.1.6     | Transition Zone, Rigid Area to<br>Flexible Area               |

|      | 4.1.7     | Solder Wicking/Plating Migration<br>Under Coverlayer 106      |

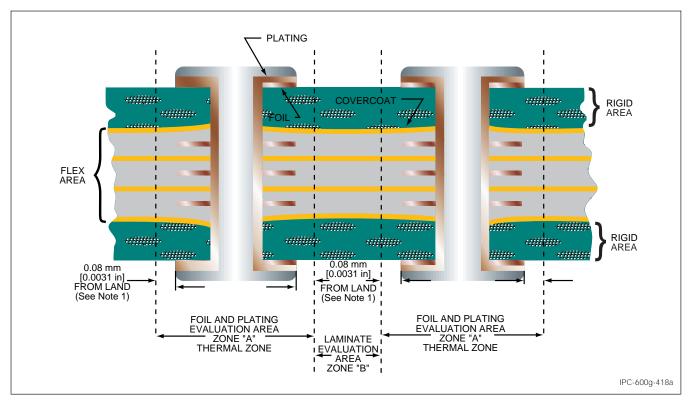

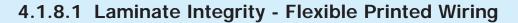

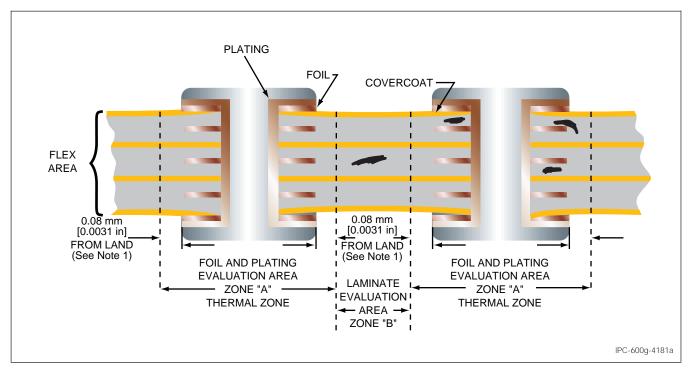

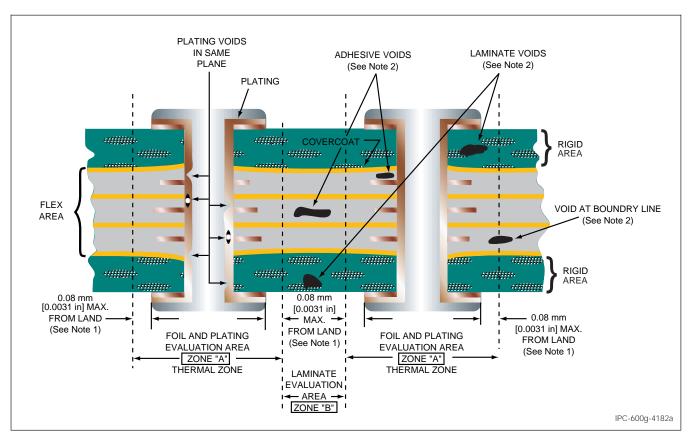

|      | 4.1.8     | Laminate Integrity 107                                        |

|      | 4.1.8.1   | Laminate Integrity - Flexible<br>Printed Wiring               |

|      | 4.1.8.2   | Laminate Integrity - Rigid-Flex<br>Printed Wiring             |

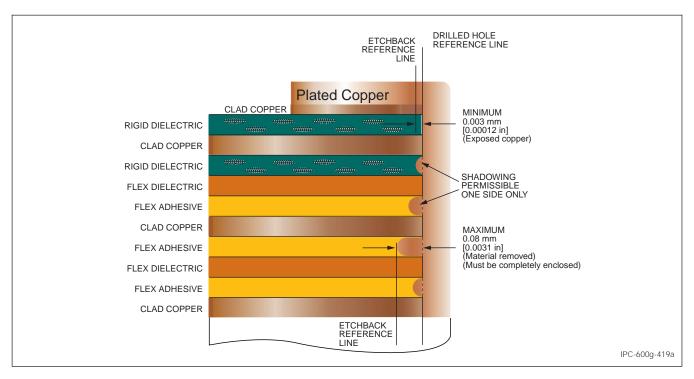

|      | 4.1.9     | Etchback (Type 3 and<br>Type 4 Only) 110                      |

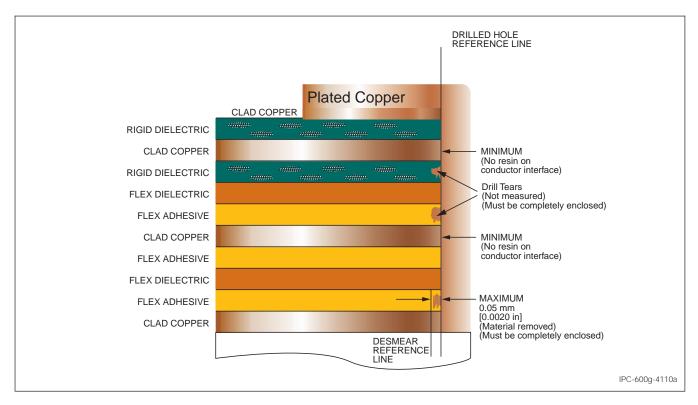

|      | 4.1.10    | Smear Removal (Type 3<br>and 4 Only) 111                      |

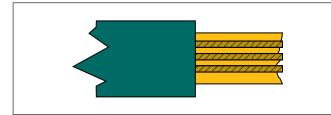

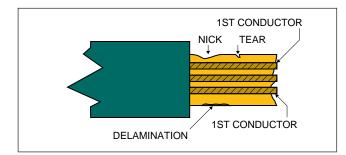

|      | 4.1.11    | Trimmed Edges/Edge<br>Delamination 112                        |

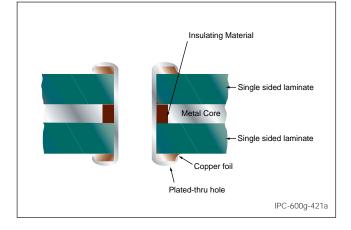

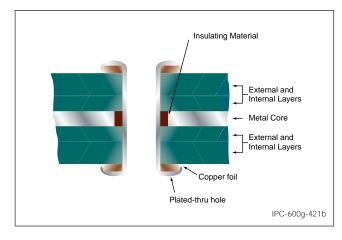

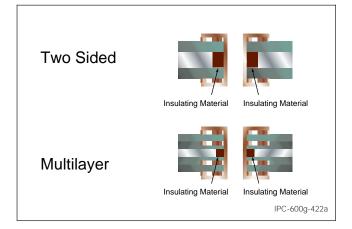

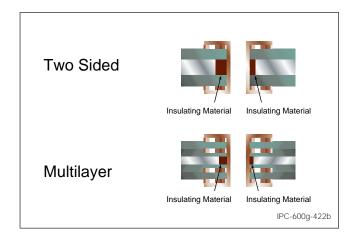

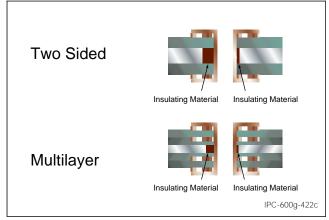

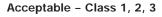

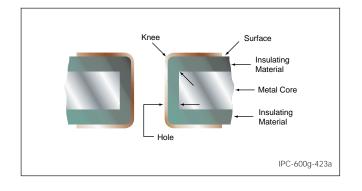

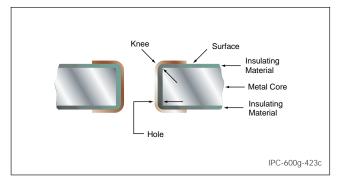

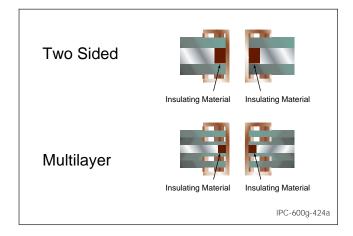

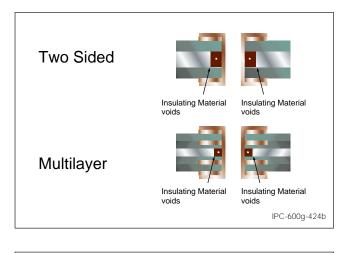

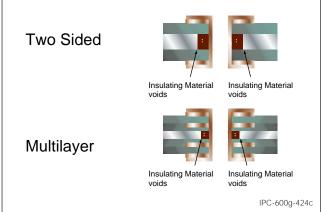

| 4.2  | Metal Co  | ore Printed Boards 113                                        |

|      | 4.2.1     | Type Classifications 114                                      |

|      | 4.2.1     | Spacing Laminated Type 115                                    |

|      | 4.2.3     | Insulation Thickness, Insulated<br>Metal Substrate            |

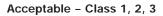

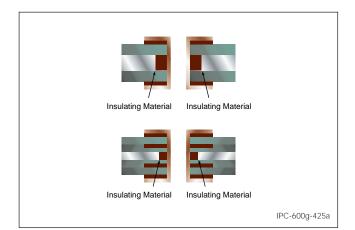

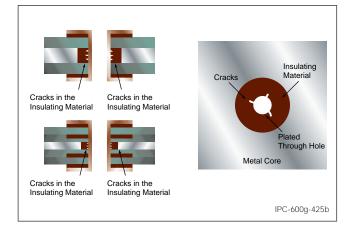

|      | 4.2.4     | Insulation Material Fill, Laminated<br>Type Metal Core 117    |

|      | 4.2.5     | Cracks in Insulation Material Fill,<br>Laminated Type         |

|      | 4.2.6     | Core Bond to Plated-Through<br>Hole Wall 119                  |

| 4.3  | Flush P   | rinted Boards 120                                             |

| -110 | 4.3.1     | Flushness of Surface Conductor 120                            |

| 5.0  |           | ess Testing 121                                               |

| 5.1  | Solderal  | bility Testing 122                                            |

| 0.1  | 5.1.1     | Plated-Through Holes 123                                      |

| 5.2  | Electrica | al Integrity 124                                              |

# Introduction

#### 1.1 SCOPE

This document describes the preferred, acceptable, and nonconforming conditions that are either externally or internally observable on printed boards. It represents the visual interpretation of minimum requirements set forth in various printed board specifications, i.e.; IPC-6010 series, ANSI/J-STD-003, etc.

#### 1.2 PURPOSE

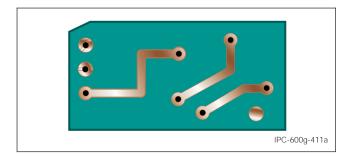

The visual illustrations in this document portray specific criteria of the requirements of current IPC specifications. In order to properly apply and use the content of this document, the printed wiring product should comply with the design requirements of the applicable IPC-2220 series document and the performance requirements of the applicable IPC-6010 series document. In the event the printed wiring product does not comply with these or equivalent requirements, then the acceptance criteria should be as defined between a user and supplier agreement as part of the procurement documentation.

The illustrations in this document portray specific criteria relating to the heading and subheading of each page, with brief descriptions of the acceptable and nonconforming conditions for each product class. (See 1.4 Classification.) The visual quality acceptance criteria are intended to provide proper tools for the evaluation of visual anomalies. The illustrations and photographs in each situation are related to specific requirements. The characteristics addressed are those that can be evaluated by visual observation and/or measurement of visually observable features.

Supported by appropriate user requirements, this document should provide effective visual criteria to quality assurance and manufacturing personnel.

This document cannot cover all of the reliability concerns encountered in the printed board industry; therefore, attributes not addressed in this issue **shall** be agreed upon between user and supplier. The value of this document lies in its use as a baseline document that may be modified by expansions, exceptions, and variations which may be appropriate for specific applications.

This is a document for minimum acceptability requirements and is not intended to be used as a performance specification for printed board manufacture or procurement.

In the event of a conflict between the requirements of this document and the applicable product performance specification, the following precedence **shall** be used:

- a) Approved Printed Board Procurement Document

- b) Generic Specifications

- c) Applicable Performance Specification

- d) Acceptability of Printed Boards (IPC-A-600)

When making accept and/or reject decisions, the awareness of documentation precedence must be maintained.

This document is a tool for observing how a product may deviate due to variation in processes. Refer to IPC-9191.

IPC-A-600 provides a useful tool for understanding and interpretating Automated Inspection Technology (AIT) results. AIT may be applicable to the evaluation of many of the dimensional characteristics illustrated in this document.

#### **1.3 APPROACH TO THIS DOCUMENT**

Characteristics are divided into two general groups:

- Externally Observable (Section 2)

- Internally Observable (Section 3)

**"Externally observable"** conditions are those features or imperfections which can be seen and evaluated on or from the exterior surface of the board. In some cases, such as voids or blisters, the actual condition is an internal phenomenon and is detectable from the exterior.

"Internally observable" conditions are those features or imperfections that require microsectioning of the specimen or other forms of conditioning for detection and evaluation. In some cases, these features may be visible from the exterior and require microsectioning in order to assess acceptability requirements.

Specimens should be illuminated during evaluation to the extent needed for effective examination. The illumination should be such that no shadow falls on the area of interest except those shadows caused by the specimen itself. It is recommended that polarization and/or dark field illumination be employed to prevent glare during the examination of highly reflective materials.

#### 1.4 CLASSIFICATION

This document recognizes that the acceptable extent of imperfection for specific characteristics of printed boards may be determined by the intended end use. For this reason, three general classes have been established based on functional reliability and performance requirements.

**Class 1** — General Electronic products: Includes consumer products, some computer and computer peripherals suitable for applications where cosmetic imperfections are not important, and the major requirement is function of the completed printed board.

**Class 2** — Dedicated Service Electronic Products: Includes communications equipment, sophisticated business machines, and instruments where high performance and

# Introduction (cont.)

extended life is required, and for which uninterrupted service is desired, but is not critical. Certain cosmetic imperfections are allowed.

**Class 3** — High Reliability Electronics Products: Includes equipment and products where continued performance or performance on demand is critical. Equipment downtime cannot be tolerated, and the equipment must function when required, such as life support systems or flight control systems. Printed boards in this class are suitable for applications where high levels of assurance are required and service is essential.

Acceptability criteria in this document have been separated so that printed board product may be evaluated to any one of the three classes. The use of one class for a specific characteristic does not mean that all other characteristics must meet the same class. Selection should be based on minimum need. The customer has the ultimate responsibility for identifying the class to which the product is evaluated. Thus, accept and/or reject decisions must be based on applicable documentation such as contracts, procurement documentation, specifications, standards and reference documents.

Requirement exceptions commonly used for industry segments such as Space and Military Avionics are described within Performance Specification Sheets in IPC-6012 and are designated as Class 3/A, Class 3/B, etc. The scope of IPC-A-600 does not include illustrations for these requirement exceptions and the user is encouraged to substitute text in IPC-A-600 with the requirements for these Performance Specification Sheets where applicable based on the corresponding subsection in IPC-6012.

#### **1.5 ACCEPTANCE CRITERIA**

Most of the illustrations and photographs included in this document represent three levels of quality for each specific characteristic; i.e., Target Condition, Acceptable and Nonconforming. The text included with each level establishes the "Acceptance Criteria" for each class of product.

*Target Condition* depicts the desired condition. This condition may not be necessary to ensure the reliability of the board in its service environment.

**Acceptable** indicates that the condition depicted, while not necessarily perfect, will maintain the integrity and reliability of the board in its service environment. The acceptable condition is considered acceptable for at least one or more classes but may not be acceptable for all classes, as specified by the associated acceptance criteria.

**Nonconforming** indicates that the condition depicted may be insufficient to ensure the reliability of the board in its service environment. The nonconforming condition is considered

unacceptable for at least one or more classes of product but may be acceptable for other classes as specified by the associated acceptance criteria.

The target, acceptable and nonconforming conditions depicted herein and the associated acceptance criteria are intended to represent typical industrial practices. Requirements of individual product designs may deviate from these criteria.

The examples shown in the photographs and/or illustrations are sometimes exaggerated to make the referenced imperfection more apparent. The relationship between the text and the examples is not always parallel; it would be difficult to find many cases so specific that they would always match the acceptance criteria. When photographs or illustrations contained in this standard are not consistent with discussion in the written Text, the written text takes precedence and should be followed.

It should also be noted that some of the photographs used may have more than one type of condition on the same example. It is necessary that the users of this document pay particular attention to the subject of each section to avoid misinterpretation.

It should be understood that the first inference to nonconformance given implies that all other conditions of lesser magnitude are acceptable. Thus, a criteria which states a nonconformance condition as 50% of the surface is pitted, for example, implies that anything less than 50% of the surface being pitted is acceptable for that characteristic in that class. Obviously, nonconformance in Class 1 implies nonconformance in Classes 2 and 3; and likewise, nonconformance for Class 2 implies nonconformance in Class 3.

An inspector **shall not** make the selection as to which class the part under inspection belongs. When making accept and/or nonconformance decisions, the awareness of precedence of documentation must be maintained, i.e., typically contract, procurement documentation, specifications and referenced documents.

In all cases, documentation should be available to the inspector defining to which class the part submitted for inspection belongs.

Procedures and requirements for conducting visual inspections related to this document **shall** be in accordance with the requirements of the applicable performance specification.

In the event of conflict, the following order of precedence **shall** apply:

- 1. Procurement documentation.

- 2. Procurement documentation reflecting the customers detailed requirements.

# Introduction (cont.)

- 3. Other documents to the extent specified by the customer.

- 4. The end item performance specification such as the IPC-6010 series when invoked by the customer.

- 5. This acceptability document.

Printed boards should be of uniform quality and **shall** conform to the IPC-6010 series.

IPC-6010 series establishes the minimum acceptability requirements for printed boards. This document, IPC-A-600, is a companion and complementary document, providing pictorial interpretation of these requirements.

IPC-A-600 can be used as a support document for inspection. It does not specify frequency of in-process inspection or frequency of end product inspection. Nor is the allowable number of nonconforming process indicators or the number of allowable repair/rework of defects specified.

Visual examination for applicable attributes **shall** be conducted at 3 diopters (approximately 1.75X). If the acceptable condition of a suspected defect is not apparent, it should be verified at progressively higher magnifications (up to 40X) to confirm that it is a defect. Dimensional requirements such as spacing or conductor width measurements may require other magnifications and devices with reticles or scales in the instrument, which allow accurate measurements of the specified dimensions. Contract or specification may require other magnifications.

Plated-through holes **shall** be internally examined for foil and plating integrity at a magnification of 100X. Referee examinations **shall** be accomplished at a magnification of 200X.

Automated Inspection Technology (AIT) results may be applicable to the evaluation of many of the dimensional characteristics illustrated in this document.

#### 1.6 APPLICABLE DOCUMENTS<sup>1</sup>

The following documents form a part of this document to the extent specified herein. The revision of the document in effect at the time of solicitation **shall** take precedence.

J-STD-003 Solderability Tests for Printed Boards

**IPC-T-50** Terms and Definitions for Interconnecting and Packaging Electronic Circuits

IPC-TM-650 Test Methods Manual<sup>2</sup>

2.1.1E 05/04 Microsectioning

| atic<br>ter- |

|--------------|

|              |

|              |

| ble          |

| mi-          |

|              |

|              |

|              |

| ape          |

|              |

|              |

**IPC-SM-840** Qualification and Performance of Permanent Solder Mask

IPC-2220 Series of Design Standards for Printed Boards

**IPC-6010** Series of Performance Specifications for Printed Boards

**IPC-9191** General Requirements for Implementation of Statistical Process Control

#### 1.7 DIMENSIONS AND TOLERANCES

All dimensions and tolerances specified herein are applicable only to the end product. Dimensions are expressed in hard SI (metric) units and parenthetical soft imperial [inch] units.

Reference information is shown in parentheses ().

#### **1.8 TERMS AND DEFINITIONS**

Terms and definitions shall be in accordance with IPC-T-50.

#### 1.9 WORKMANSHIP

Printed boards fabricated to the requirements of this document **shall** be processed in such a manner as to be uniform in quality and to preclude the introduction of dirt, foreign matter, oil, fingerprints, flux residues, or other contaminants that may affect the life or serviceability of the product. Printed boards **shall** be free of defects in excess of those allowed by this document. Acceptance of imperfections not specifically covered by this document **shall** be agreed upon by the user and supplier of the product.

<sup>1.</sup> www.ipc.org

Current and revised IPC Test Methods are available through IPC-TM-650 subscription and on the IPC Web site (www.ipc.org/html/testmethods.htm).

### Introduction

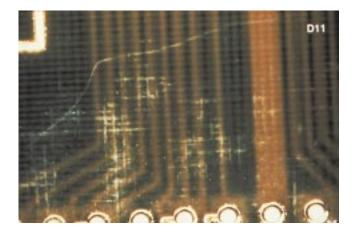

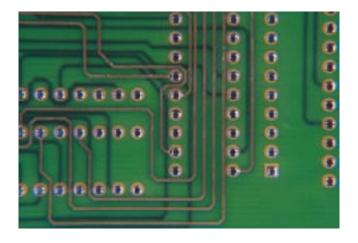

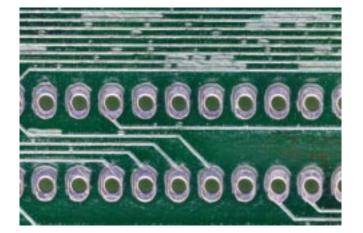

This section addresses those characteristics which are observable from the surface. This includes those characteristics that are external and internal in the printed board but visible from the surface as follows:

- Surface Imperfections such as burrs, nicks, scratches, gouges, cut fibers, weave exposure and voids.

- Subsurface Imperfections such as foreign inclusions, measling/crazing, delamination, pink ring and laminate voids.

- Imperfections in Conductive Pattern such as loss of adhesion, reduction of conductor width or thickness due to nicks, pinholes, scratches, surface plating or coating defects.

- Hole Characteristics such as diameter, misregistration, foreign material, and plating or coating defects.

- Marking Anomalies including location, size, readability, and accuracy.

- Solder Resist Surface Coating Imperfections such as misregistration, blisters, bubbles, delamination, adhesion, physical damage and thickness.

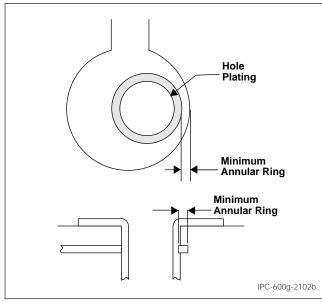

- **Dimensional Characteristics** including printed board size and thickness, hole size and pattern accuracy, conductor width and spacing, registration and annular ring.

# 2.1 Board Edges

Imperfections such as burrs, nicks or haloing along the edge of the board are acceptable provided they do not exceed the limits below.

# 2.1.1 Burrs

Burrs are characterized by small lumps or masses with an irregular shape, convex to a surface, and are a result of a machine process, such as drilling or gouging.

# 2.1.1.1 Nonmetallic Burrs

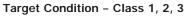

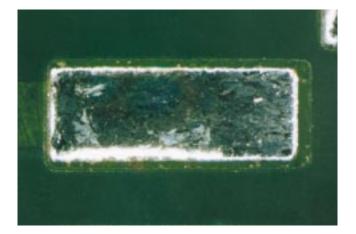

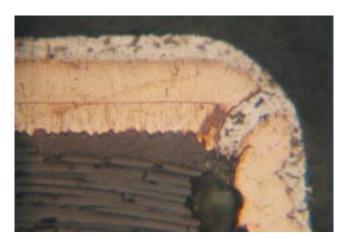

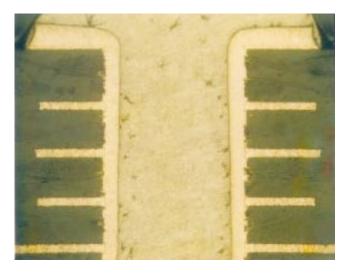

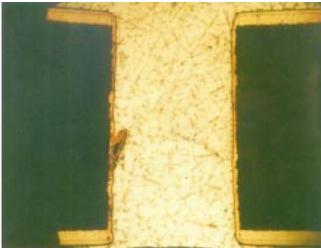

#### Target Condition – Class 1, 2, 3

• Edge conditions – smooth, no burrs.

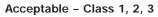

#### Acceptable - Class 1, 2, 3

- Edge conditions rough but not frayed.

- Edge conditions loose burrs do not affect fit and function.

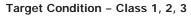

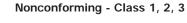

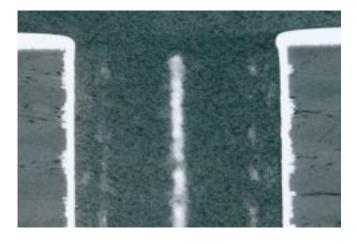

#### Nonconforming – Class 1, 2, 3

# 2.1.1.2 Metallic Burrs

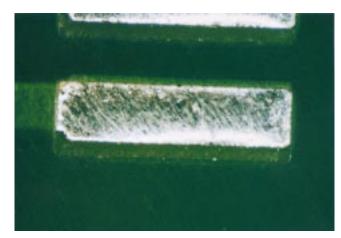

#### Target Condition – Class 1, 2, 3

• Edge condition - smooth, no burrs.

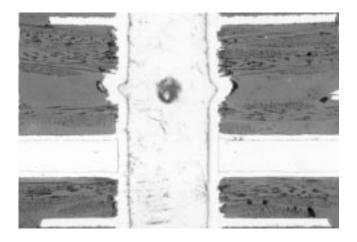

# Acceptable - Class 1, 2, 3Edge condition - rough but not frayed.

• Edge condition - no loose burrs.

# 2

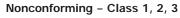

#### Nonconforming – Class 1, 2, 3

#### 2.1 BOARD EDGES

# 2.1.2 Nicks

• Edge condition - smooth, no nicks.

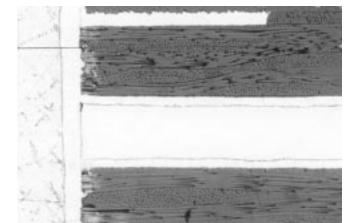

#### Acceptable - Class 1, 2, 3

- Edges are rough but not frayed.

- Nicks do not extend more than 50% of the distance from the edge of the board to the closest conductor or are greater than 2.5 mm [0.0984 in] whichever is less.

#### Nonconforming – Class 1, 2, 3

#### 2.1 BOARD EDGES

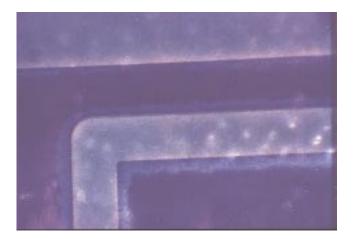

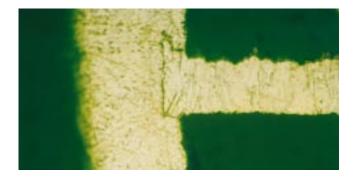

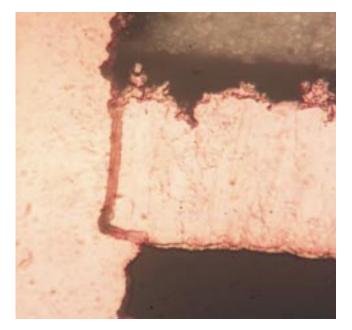

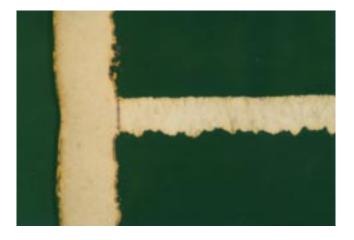

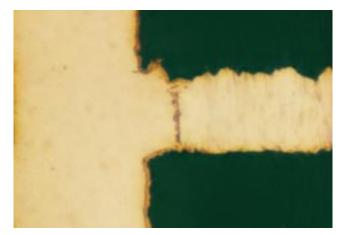

# 2.1.3 Haloing

# Target Condition – Class 1, 2, 3

• No haloing.

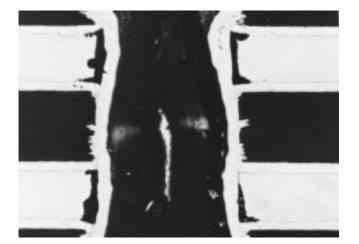

#### Acceptable - Class 1, 2, 3

• Penetration of haloing does not reduce the unaffected distance from the board edge to the closest conductive pattern by more than 50% or more than 2.5 mm [0.0984 in], whichever is less.

#### Nonconforming - Class 1, 2, 3

# Introduction

#### Identification of Imperfections

Much confusion has existed in the industry regarding the identification of defects that exist in laminates. To help identify those conditions, refer to the following sections where definitions, illustrations and photographs have been provided which precisely define and identify the following conditions:

#### Surface 2.2

| weave exposure                               | 2.2.1          |

|----------------------------------------------|----------------|

| weave texture                                | 2.2.2          |

| <ul> <li>exposed/disrupted fibers</li> </ul> | 2.2.3          |

| <ul> <li>pits and voids</li> </ul>           | 2.2.4          |

|                                              |                |

| Subsurface 2.3                               |                |

| Subsurface 2.3 • measling                    | 2.3.1          |

|                                              | 2.3.1<br>2.3.2 |

| • measling                                   |                |

It is important to note that laminate defect conditions may exist when the fabricator receives the material from the laminator, or may become apparent during the fabrication of the printed board. Some defects may be induced during processing.

#### The Use of Acceptability Criteria

Everyone cannot be an expert on laminate defects. Some nondestructive visual criteria must be established to aid in making a decision regarding acceptability levels.

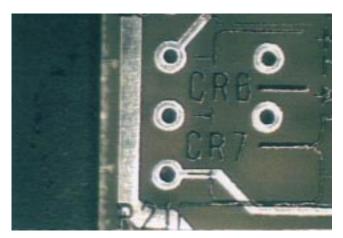

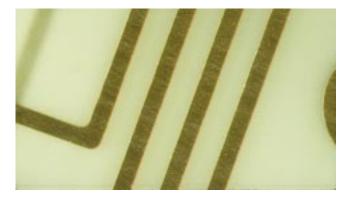

# 2.2.1 Weave Exposure

*Weave Exposure:* A surface condition of base material in which the unbroken fibers of woven cloth are not completely covered by resin.

Note: This graphic is for illustrative purposes only and does not require a microsection evaluation.

#### Acceptable - Class 1, 2, 3

• Excluding the area(s) with weave exposure, the remaining space between conductors meets the minimum conductor spacing requirement.

#### Nonconforming - Class 1, 2, 3

#### 2.2 BASE MATERIAL SURFACE

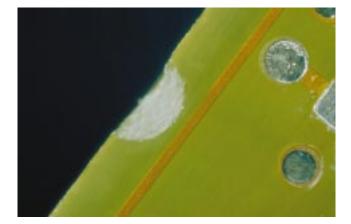

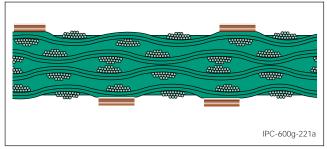

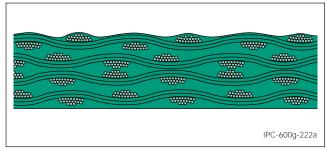

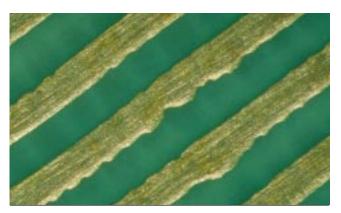

# 2.2.2 Weave Texture

*Weave Texture:* A surface condition of base material in which a weave pattern of cloth is apparent although the unbroken fibers of woven cloth are completely covered with resin.

Note: This graphic is for illustrative purposes only and does not require a microsection evaluation.

#### Acceptable - Class 1, 2, 3

• Weave texture is an acceptable condition in all classes but is sometimes confused with weave exposure because of similar appearances.

This example could be either weave exposure or weave texture. The difference cannot be determined from this view. The difference can be discerned using nondestructive tests (oblique illumination with microscope) or microsection.

# 2.2.3 Exposed/Disrupted Fibers

#### Acceptable - Class 1, 2, 3

• Exposed or disrupted fibers do not bridge conductors and do not reduce the conductor spacing below the minimum requirements.

#### Nonconforming

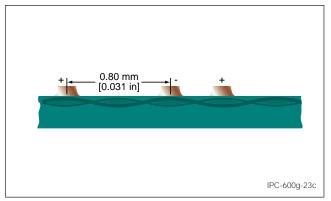

# 2.2.4 Pits and Voids

Target Condition – Class 1, 2, 3

• No pits or voids.

#### Acceptable - Class 1, 2, 3

- Pits or voids do not exceed 0.8 mm [0.031 in].

- Total board area affected is less than 5% per either side.

- Pits or voids do not bridge conductors.

#### Nonconforming - Class 1, 2, 3

## Introduction

This section is focused on those subsurface conditions of laminated base materials that are externally observable through the base material itself and some solder resist coatings. The most frequent subsurface base materials conditions are termed measling, crazing, delamination, blistering and foreign materials. These conditions may be observed throughout the printed board manufacturing and inspection process; such as:

- During incoming metal-clad base material evaluations after being manufactured by the laminator,

- By the printed board manufacturer after having removed (etched) the metal- cladding in the preparation of ''inner-layer'' details for multilayer printed boards,

- After etching the ''outer'' layers of printed boards to form the required arrangement of conductive patterns and markings,

- After baking operations (such as solder resist or component legends),

- After thermal shock, as in solder fusing/coating or solderability testing processes.

Base material subsurface conditions have been the subject of considerable discussion within the printed board industry for several decades. Of the several subsurface conditions, measling and crazing continue to cause the most concerns. Measles and crazing have been the primary focus of two IPC "Blue Ribbon Committees" of experts. The following are brief summaries and additional comments from the IPC's Blue Ribbon Committee:

# Brief summary of the First IPC Blue Ribbon Committee on Measles

The committee conducted a wide overview of printed board base material surface and subsurface conditions with a major focus on measles. IPC's "Measles in Printed Wiring Boards, Information Document'' was published in 1973 as a result of this effort. The committee was to collect as much data as was available on measles and other surface/subsurface conditions; and to standardize the terms, definitions (descriptions), photographs, and illustrations of surface and subsurface conditions. It was felt that sufficient research had been done by industry and that a position on "measles" could be prepared by the committee. The committee's recommendation was as follows, "comprehensive review of available literature and available research and test data, that while measles may be objectionable cosmetically, their effect on functional characteristics of finished products, are at worst minimal, and in most cases insignificant."

Comments: Despite the committee's recommendation and industry data, there was still a strong reluctance by most gov-

ernment and industry personnel to accept that measles are a cosmetic condition with no functional effect in most applications. Most companies continued to retain "no measling" requirements in their specifications. But when measles or other nonconforming surface/subsurface conditions had severe impact on their production schedules, the customer (or acceptance agency) would produce a document that established acceptance guidelines for measles (and frequently other surface and subsurface conditions). The new guidelines were based on size, percent reduction in conductor spacing, and amount of affected area. They also varied from customerto-customer. As technology evolved, in particular reductions in conductor spacing, the effect of measling and other surface/subsurface conditions once again became a serious industry wide concern. As a result, a second IPC Blue Ribbon Committee on Measles was formed.

# Brief summary of the Second IPC Blue Ribbon Committee on Measles

The committee was formed in late 1978. This committee reviewed the findings of the first committee, solicited the industry for additional data, and reviewed the proprietary acceptance criteria provided by IPC members. The Second Blue Ribbon Committee came to the same conclusion. Measles are a cosmetic process indicator and had almost no reported effects on a product's functional performance in most applications. The major exception was high voltage applications. There was still reluctance by some government organizations and a few industrial companies to categorically accept measles. As such, this committee established a set of measling/crazing requirements that obtained consensus from all IPC members. The result was a matrix of acceptance limitations for the three major phases of the printed board electronic assembly process: laminated material, printed board final inspection, and after printed board assembly. These requirements included percent reductions in conductor spacing (not exceeding minimum conductor spacing), and various amounts of measled area for each side of the printed board (or assembly) based on the Class of product. These requirements were added as an amendment to the first printing of the IPC-A-600, Revision C, and were included in later printings of the C revision and, in a different format, the IPC-A-600, Revision D.

Comments: The primary concerns expressed by the reluctant individuals are summarized in the following list (with comments):

• Electrical Insulation Resistance, both volume and surface several reports and available test data indicates that insulation resistance is not significantly affected by measling or crazing.

# Introduction (cont.)

- Contamination the concern was that ionic materials could diffuse or be ''pumped'' (by alternating atmospheric pressure) into measles or crazing and would result in lower insulation resistance or conductive-anodic filament (CAF) growths, shorts. Salt spray tests indicated this was not a valid premise, and most ionic materials (such as salts) will not diffuse into the base material.

- Applied Voltages high voltage applications are a concern (in particular where there is the possibility of "corona" in the measling or crazing) the dielectric strength is reduced by 20-50% in comparison to a similar nonmeasled/crazed area, in particular at altitudes greater than 20 km [12.43 miles].

- Environmental most measling/crazing did not appear to increase in size or occurrence due to environmental testing.

IPC-A-600, Revision E, was the first revision to reflect the needs for surface mounted component technology. As such, the acceptance requirements for measling and crazing were separated. For measles, the acceptance requirements allowed bridging under surface conductor spacing. This was done based on the definition of measles, test data, and industry experience of measles having never been documented to cause a functional failure. Crazing is much less controlled separation in the base material forming "interconnections" between measles and possibly adjacent conductive patterns; therefore, the acceptance requirements for crazing were set the same as the similar conditions of delamination and blistering.

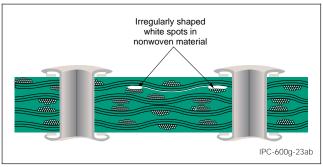

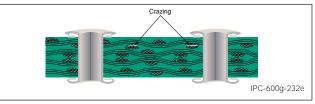

Over a period of time, governing specifications have become excessively heavy regarding the presence of measles. In addition, cosmetic appearance has become a major acceptance criterion. In actual fact, no failure has ever been attributed to measling, based on all military and industry testing to date. IPC, industry and various military agencies have conducted extensive testing in severely measled assemblies under extreme environmental conditions for long periods of time with no evidence of growth, spreading or any detriment to the function of the assembly. Measles should not be the cause for rejection. Measling is an internal condition occurring in the woven fiber reinforced laminated base material in which the bundles are separated at the weave intersection. The term "crazing" is sometimes used to describe an array of measles which appear from the surface to be interconnected. When the measles look to be interconnected, this condition called "crazing" is a form of delamination in that there are separations along the length of the fiber/yarns and the resin. For nonwoven material, this condition resembles a measle but is randomly located and has an irregular shape (see Figure 1).

In a case study done, the prime cause of the observed measles was a combination of moisture, which diffuses readily into epoxy-glass, and component soldering temperatures. The application of local high temperatures for component mounting caused entrapped moisture to vaporize and break the epoxy-glass bond at the ''knuckle'' (intersection of the warp and fill of the e-glass cloth). From previous experience, it is known that epoxy-glass absorbs atmospheric moisture, and when moisture content exceeds 0.3 wt%, it can give rise to measling during solder dip/level and/or assembly soldering operations.

There are other factors that can contribute to measles/crazing such as: resin composition, method of making laminates, coupling agents,  $T_g$ , etc. In the past, reports were compiled which revealed that measles and crazing with over 50% spacing violation were not adverse to the reliability of the hardware. Why, if all test reports showed no problems with measles and no reported field failures, are we so concerned about measles and crazing? Because it appears feasible, in theory, that if measles with 100% conductor spacing violation combines with moisture or some other contaminant, copper migration (Insulation resistance, or IR, failures) should be experienced between conductors.

Even when the potential failure mechanism mentioned above is analyzed, it is almost impossible to experience such insulation resistance (IR) or migration failure. First, a measle(s) gapping conductive patterns is needed. Secondly, moisture in the printed board/assembly, along with a conductive or ionic contaminant such as chlorides, is necessary.

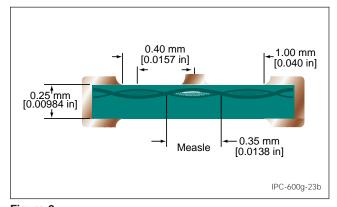

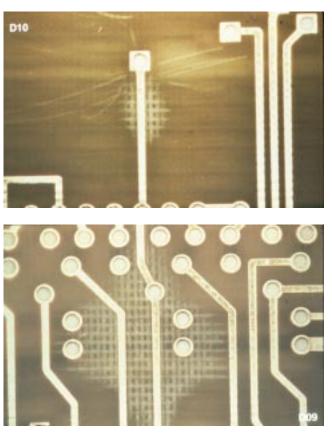

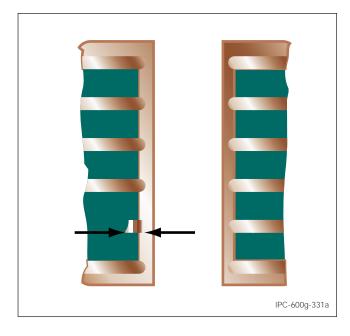

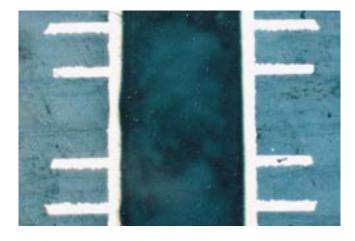

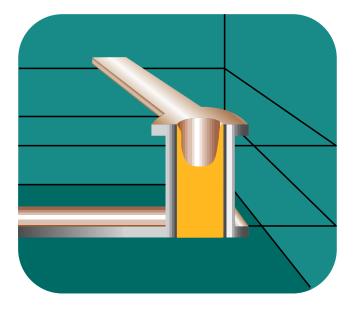

# Introduction (cont.)

In this instance, a typical industry example, the measle is at the center between two plated through holes (see Figure 2). The measle is 0.35 mm [0.0138 in] wide. In order to get possible copper migration, the measle had to gap the two plated through holes. This of course would be most unlikely. The second example (see Figure 3) illustrates what is required for a potential failure mechanism between two surface conductors. A (+) conductor directly over a knuckle is required and a (-) conductor is also required directly over a knuckle. For an electrical short to occur between these conductors through the base material, there would need to be a conductive path from one conductive pattern, through the remaining dielectric materials (resin and yarn) to the separation (measle), along the separation in the direction of the other conductive pattern, once again through the remaining dielectric materials (resin and yarn), and to the second conductive pattern. In order to induce a failure all of the above mentioned ingredients are required along with a voltage potential between two adjacent conductors. This occurrence is highly unlikely and is most likely why the industry has not experienced any adverse reliability problems due to measles.

When making acceptance calls on electronic hardware, consider all the possible concerns mentioned above. Measles should not be considered a nonconforming condition. It should instead be considered a process indicator, telling you that the process is on the verge of going out of control. Correct the problem, but do not scrap the product, taking into account all of the above mentioned variables.

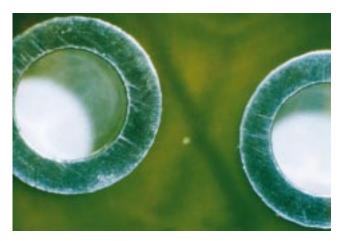

Figure 1

Note: This graphic is for illustrative purposes only and does not require a microsection evaluation.

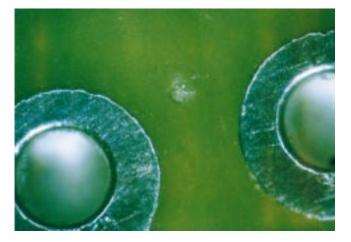

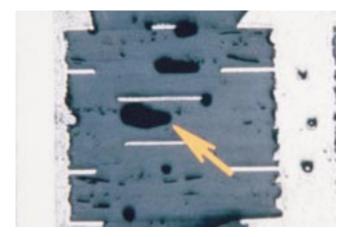

Figure 2 Note: This graphic is for illustrative purposes only and does not require a microsection evaluation.

#### Figure 3

Note: This graphic is for illustrative purposes only and does not require a microsection evaluation.

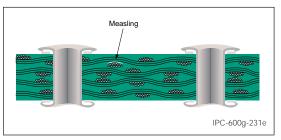

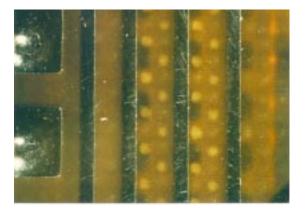

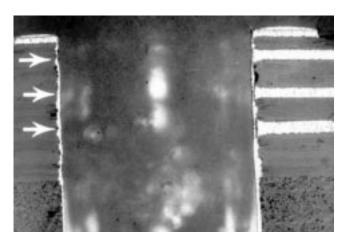

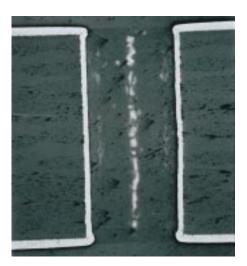

# 2.3.1 Measling

**Measling:** Measling manifests itself in the form of discrete white squares or "crosses" below the surface of the base material, and is usually related to thermally induced stress. Measles are subsurface phenomena that have been found in new laminated materials and in every board type made from woven fiber reinforced laminates at one time or another. Since measles are strictly subsurface phenomena and occur as a separation of fiber bundles at fiber bundle intersections, their apparent positions relative to surface conductors have no significance.

Note: This graphic is for illustrative purposes only and does not require a microsection evaluation.

#### Acceptable – Class 1, 2, 3

• Measles are acceptable for all products, except for high-voltage applications as defined by the customer.

Note: Measles are observed from the surface. Cross-sections are for illustration purposes only.

#### 2.3 BASE MATERIAL SUBSURFACE

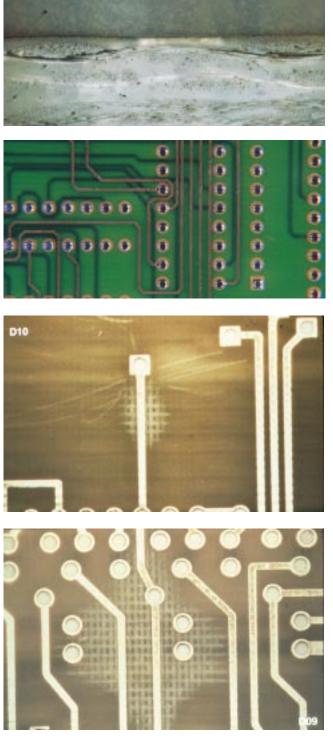

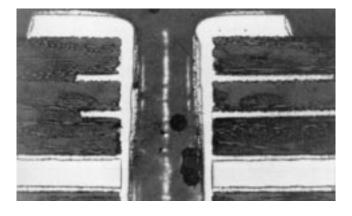

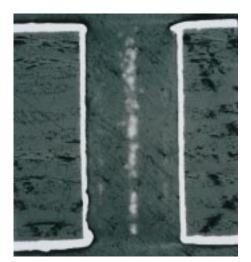

# 2.3.2 Crazing

Crazing: An internal condition occurring in the laminated base material in which the fibers within the yarn are separated. This can occur at the weave intersections or along the length of the yarn. This condition manifests itself in the form of connected white spots or "crosses" below the surface of the base material, and is usually related to mechanically induced stress. When the crosses are connected the condition is evaluated as follows:

Note: This graphic is for illustrative purposes only and does not require a microsection evaluation.

#### Target Condition - Class 1, 2, 3

• No evidence of crazing.

#### Acceptable - Class 2, 3

- The imperfection does not reduce the space between conductive patterns below the minimum conductor spacing.

- The distance of crazing does not span more than 50% of the distance between adjacent conductive patterns that are not electrically common.

- No propagation as a result of thermal testing that replicates the manufacturing process.

- · Crazing at the edge of the board does not reduce the minimum distance between board edge and conductive pattern; or more than 2.5 mm [0.0984 in] if not specified.

#### Acceptable – Class 1

- The imperfection does not reduce the space between conductive patterns below the minimum conductor spacing.

- No propagation as a result of thermal testing that replicates the manufacturing process.

- · Crazing at the edge of the board does not reduce the minimum distance between board edge and conductive pattern; or more than 2.5 mm [0.0984 in] if not specified.

#### Nonconforming - Class 1, 2, 3

Defects either do not meet or exceed above criteria.

Note: Crazing is observed from the surface. Cross-sections are for illustration purposes only.

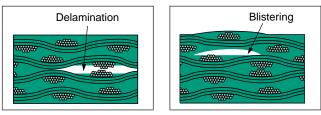

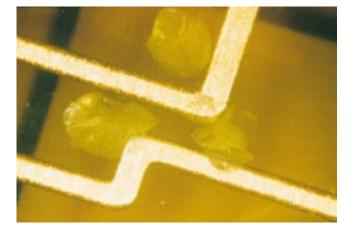

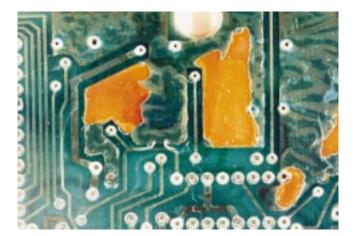

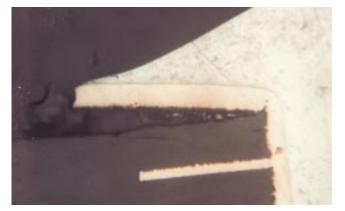

# 2.3.3 Delamination/Blister

**Delamination:** A separation between plies within a base material, between a material and conductive foil, or any other planar separations within a printed board.

**Blister:** Delamination in the form of a localized swelling and separation between any of the layers of a lamination base material, or between base material and conductive foil or protective coating.

Note: This graphic is for illustrative purposes only and does not require a microsection evaluation.

Target Condition – Class 1, 2, 3

• No blistering or delamination.

#### Acceptable - Class 2, 3

- The area affected by imperfections does not exceed 1% of the board area on each side.

- The imperfection does not reduce the space between conductive patterns below the minimum conductor spacing.

- The blister or delamination does not span more than 25% of the distance between adjacent conductive patterns.

- No propagation as a result of thermal testing that replicates the manufacturing process.

- Are no closer to the edge of the board than the specified minimum distance between board edge and conductive pattern; more than 2.5 mm [0.0984 in] if not specified.

#### Acceptable – Class 1

- The area affected by imperfections does not exceed 1% of the board area on each side.

- The blister or delamination spans more than 25% of the distance between conductors, but does not reduce the space between conductor patterns below the minimum conductor spacing.

- No propagation as a result of thermal testing that replicates the manufacturing process.

- Are no closer to the edge of the board than the specified minimum distance between board edge and conductive pattern; more than 2.5 mm [0.0984 in] if not specified.

#### Nonconforming - Class 1, 2, 3

• Defects either do not meet or exceed above criteria.

*Note:* The area affected is determined by combining the area of each imperfection and dividing by the total area of the printed board. A separate determination is made for each side.

# 2.3.4 Foreign Inclusions

Foreign Particles: Metallic or nonmetallic, which may be entrapped or embedded in an insulating material.

Foreign material may be detected in raw laminate, prepreg (B stage), or processed multilayer printed boards. The foreign objects may be conductive or nonconductive, both types may be nonconforming depending on size and location.

#### Target Condition - Class 1, 2, 3

• No foreign inclusions.

#### Acceptable - Class 1, 2, 3

- Translucent particles trapped within the board **shall** be acceptable.

- Opaque particles trapped within the board **shall** be acceptable provided the particle does not reduce the spacing between adjacent conductors to below the minimum spacing specified in the IPC-6010 series.

- Electrical parameters of the board are unaffected.

#### Nonconforming – Class 1, 2, 3

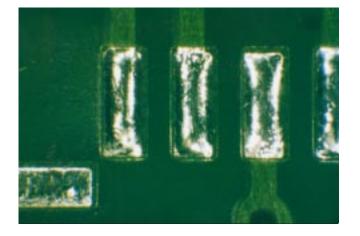

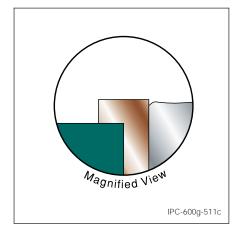

#### 2.4 SOLDER COATINGS AND FUSED TIN LEAD

# 2.4.1 Nonwetting

#### Target Condition - Class 1, 2, 3

• No nonwetting.

#### Acceptable - Class 1, 2, 3

• Complete wetting on all conductive surfaces where solder is not excluded by resist or other plating finish. Vertical sides (conductor and land) areas may not be covered.

#### Nonconforming - Class 1, 2, 3

#### 2.4 SOLDER COATINGS AND FUSED TIN LEAD

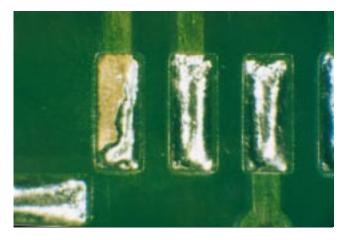

# 2.4.2 Dewetting

# No dewetting.

Target Condition - Class 1, 2, 3

#### Acceptable - Class 2, 3

- On conductors and ground or voltage planes.

- On 5% or less of each land area for solder connection.

#### Acceptable – Class 1

- On conductors and ground or voltage planes.

- On 15% or less of each land area for solder connection.

#### Nonconforming - Class 1, 2, 3

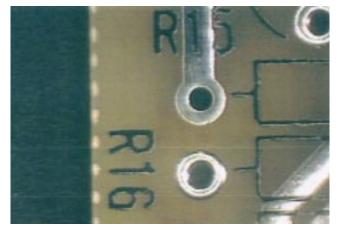

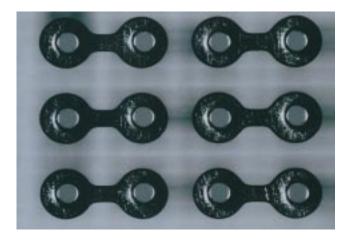

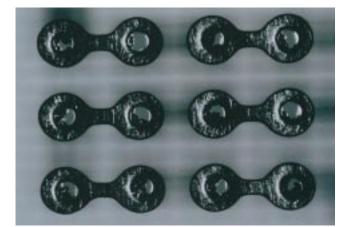

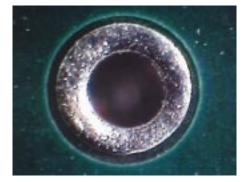

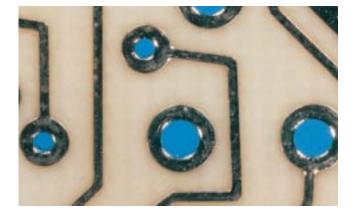

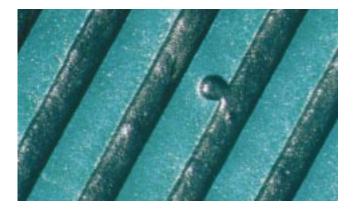

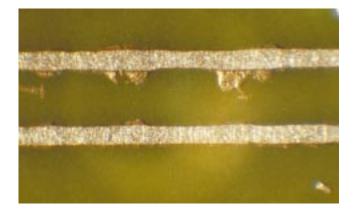

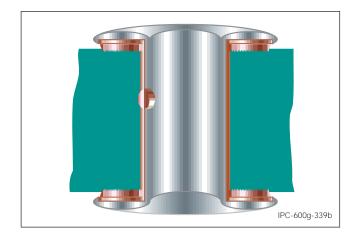

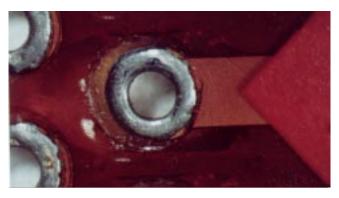

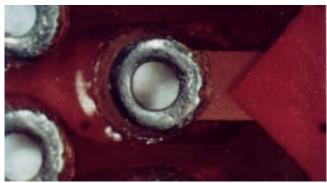

# 2.5.1 Nodules/Burrs

- Target Condition Class 1, 2, 3

- No evidence of nodules or burrs.

- Acceptable Class 1, 2, 3

- Allowed if minimum finished hole diameter is met.

- Nonconforming Class 1, 2, 3

- Defects either do not meet or exceed above criteria.

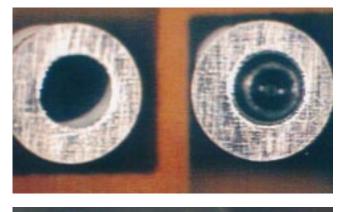

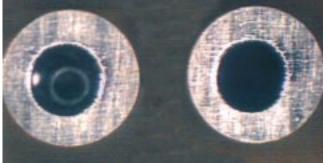

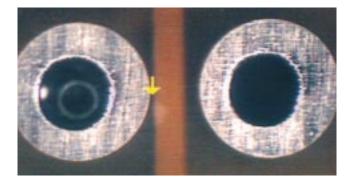

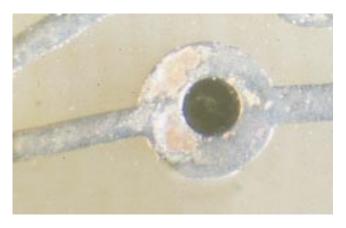

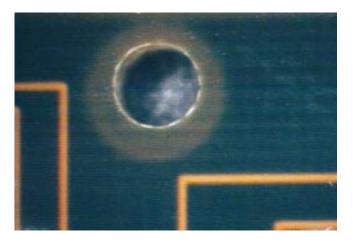

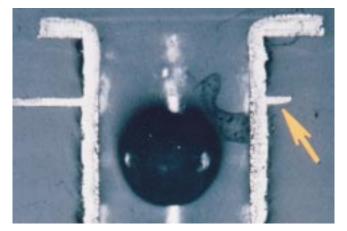

# 2.5.2 Pink Ring

#### Acceptable - Class 1, 2, 3

• No evidence exists that pink ring affects functionality. The presence of excessive pink ring may be considered a process indicator but is not nonconforming. The focus of concern should be the quality of the lamination bond and hole cleaning and conditioning processes.

#### 2.5 HOLES - PLATED-THROUGH - GENERAL

# 2.5.3 Voids – Copper Plating

# Target Condition – Class 1, 2, 3

No voids

#### Acceptable – Class 3

• No evidence of voids in the hole.

#### Acceptable - Class 2

- No more than one void in any hole.

- Not more than 5% of the holes have voids.

- Any void is not more than 5% of the hole length.

- The void is less than 90° of the circumference.

#### Acceptable - Class 1

- No more than three voids in any hole.

- Not more than 10% of the holes have voids.

- Any void is not more than 10% of the hole length.

- All voids are less than 90° of the circumference.

#### Nonconforming - Class 1, 2, 3

# 2.5.4 Voids – Finished Coating

Target Condition – Class 1, 2, 3 • No voids

#### Acceptable – Class 3

- No more than one void in any hole.

- Not more than 5% of the holes have voids.

- The void is not more than 5% of the hole length.

- The void is less than 90° of the circumference.

#### Acceptable – Class 2

- No more than three voids in any hole.

- Not more than 5% of the holes have voids.

- Any void is not more than 5% of the hole length.

- All voids are less than 90° of the circumference.

#### Acceptable – Class 1

- No more than five voids in any hole.

- Not more than 15% of the holes have voids.

- Any void is not more than 10% of the hole length.

- $\bullet$  All voids are less than 90° of the circumference.

#### Nonconforming - Class 1, 2, 3

#### 2.5 HOLES - PLATED-THROUGH - GENERAL

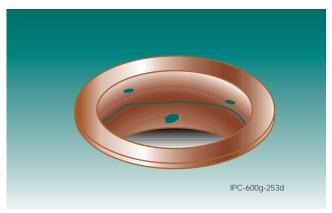

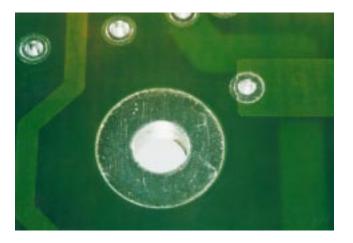

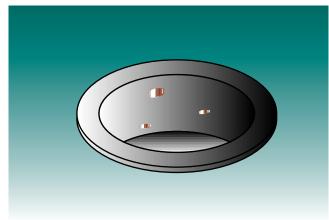

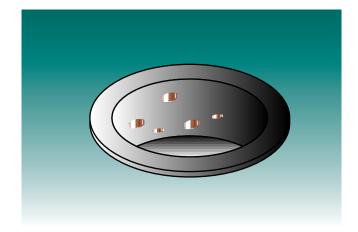

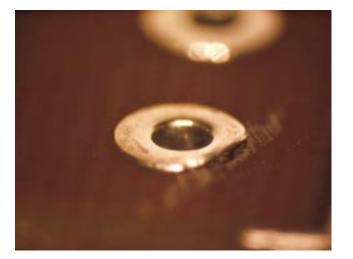

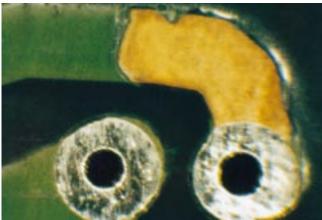

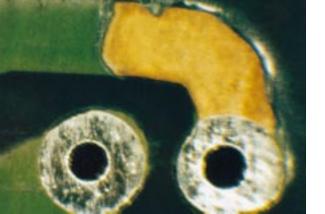

# 2.5.5 Lifted Lands - (Visual)

Target Condition/Acceptable - Class 1, 2, 3

• No lifting of lands.

#### Nonconforming - Class 1, 2, 3

#### 2.6 HOLES - UNSUPPORTED

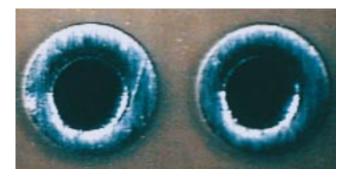

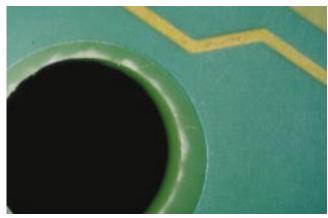

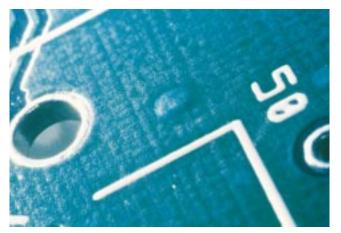

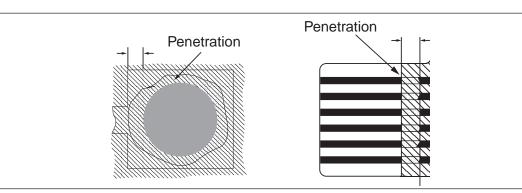

# 2.6.1 Haloing

*Haloing:* Mechanically induced fracturing or delamination on or below the surface of the base material; a light area around the holes, other machined areas or both are usually indications of haloing. See also 2.1.3.

#### Target Condition - Class 1, 2, 3

• No haloing.

#### Acceptable - Class 1, 2, 3

• Penetration of haloing does not reduce the unaffected distance from the board edge to the closest conductive pattern by more than 50% or more than 2.5 mm [0.0984 in], whichever is less.

#### Nonconforming – Class 1, 2, 3

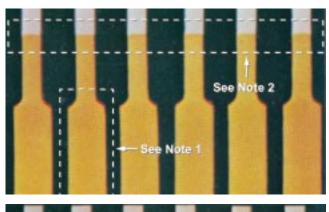

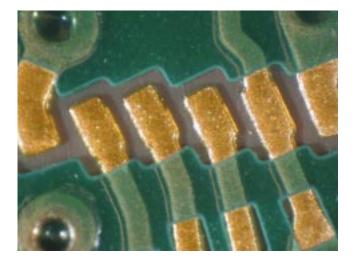

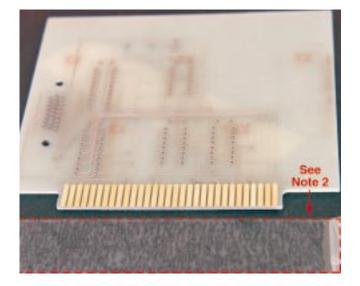

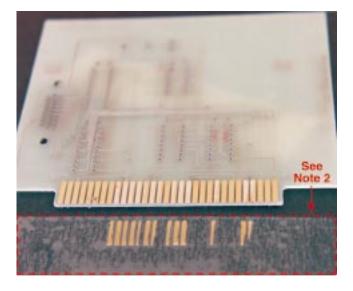

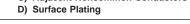

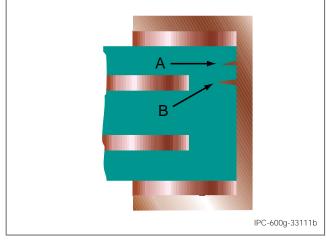

# 2.7.1 Surface Plating – General

#### Target Condition - Class 1, 2, 3

- · Contacts are free of pits, pinholes and surface nodules.

- No exposed copper or plating overlap between solder finish or solder mask and tip finish.

#### Acceptable - Class 1, 2, 3 (Critical Contact Area)

- Surface defects do not expose underlying metal in critical contact area.

- Solder splashes or tin-lead plating does not occur in critical contact area.

- No nodules and metal bumps in critical contact area.

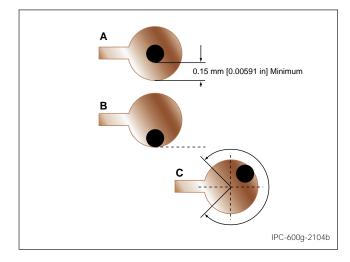

- Pits, dents or depressions do not exceed 0.15 mm [0.00591 in] in their longest dimension. There are not more than three per contact, and they do not appear on more than 30% of the contacts.

#### Acceptable - Class 3 (Gap/Overlap Area)

• Exposed copper or plating overlap is 0.8 mm [0.031 in] or less.

#### Acceptable - Class 2 (Gap/Overlap Area)

• Exposed copper or plating overlap does not exceed 1.25 mm [0.04921 in].

#### Acceptable - Class 1 (Gap/Overlap Area)

• Exposed copper or plating overlap does not exceed 2.5 mm [0.0984 in].

#### Nonconforming - Class 1, 2, 3

• Defects either do not meet or exceed above criteria.

*Note 1:* Critical contact area. These conditions do not apply to a band 0.15 mm [0.00591 in] wide around the periphery of the printed contact land.

Note 2: Discoloration is permitted in the plating overlap zone.

# 2.7.1.1 Surface Plating - Wire Bond Pads

#### Target Condition - Class 1, 2, 3

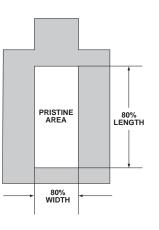

- Contacts are free of surface nodules, roughness, electrical test witness marks or scratches that exceed 0.8 µm [32 µin] RMS (root-mean-square) in the pristine area in accordance with an applicable test method as agreed between user and supplier. If IPC-TM-650, Method 2.4.15, is used, it is recommended that the roughness-width cutoff be adjusted to approximately 80% of the maximum length of the wire bond pad in order to obtain the RMS value within the pristine area. For more information on surface roughness, refer to ASME B46.1

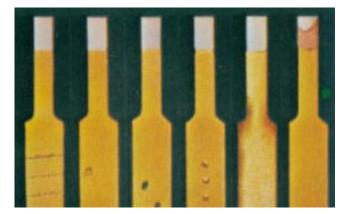

- The pristine area is defined as an area bounded in the center of the pad by 80% of the pad width and 80% of the pad length (see Figure 1).

Figure 1 Wire Bond Pad Pristine Area

#### Nonconforming – Class 1, 2, 3

#### 2.7 PRINTED CONTACTS

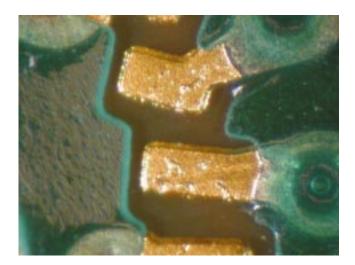

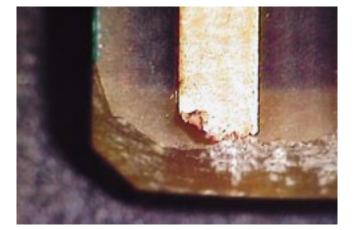

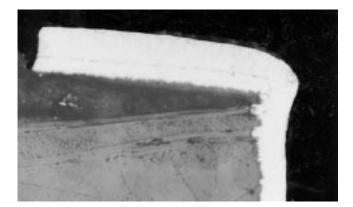

### 2.7.2 Burrs on Edge-Board Contacts

#### Target Condition - Class 1, 2, 3

• Smooth edge condition.

#### Acceptable - Class 1, 2, 3

• Edge condition - smooth, no burrs, no rough edges, no lifted plating on printed contacts, no separation (delamination) of printed contacts from the base material, and no loose fibers on the beveled edge. Exposed copper at end of printed contact is expected and permissible.

#### Nonconforming - Class 1, 2, 3

## 2.7.3 Adhesion of Overplate

#### Acceptable - Class 1, 2, 3

• Good plating adhesion as evidenced by tape test. No plating removed. If overhanging metal breaks off and adheres to the tape, it is evident of overhang or slivers, but not of plating adhesion failure.

#### Nonconforming – Class 1, 2, 3

• Defects either do not meet or exceed the above criteria.

*Note 1:* The adhesion of the plating **shall** be tested in accordance with IPC-TM-650, Method 2.4.1, using a strip of pressure sensitive tape applied to the surface and removed by manual force applied perpendicular to the circuit pattern. *Note 2:* Plating that has adhered to the tape.

#### 2.8 MARKING

### Introduction

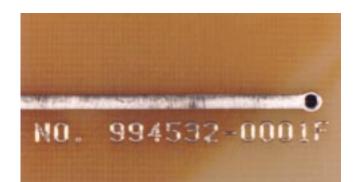

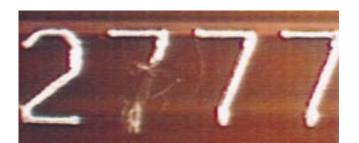

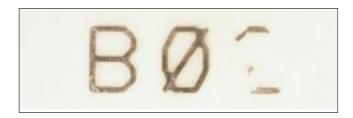

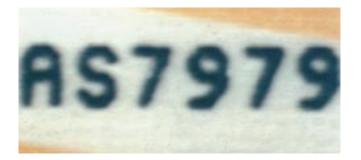

This section covers acceptability criteria for marking of printed boards. Marking of printed boards provides a means of identification and aids in assembly. Legends screened over metal will generally degrade in a solder process or stringent cleaning environments. Legends over metal are not recommended. When use of legends over solder is required, an etched legend is target condition. Minimum requirements should be specified on the procurement documentation. Examples of the marking addressed by this section are:

- Assembly or fabrication part numbers when a requirement of the procurement documentation. Each individual board, each qualification board, and each set of quality conformance test circuitry (as opposed to each individual coupon) **shall** be marked in order to ensure traceability between the boards/test circuitry and the manufacturing history and to identify the supplier (logo, etc.).

- Component insertion locators, when a requirement of the procurement documentation.

- Manufacturing sequence number when required by the work order.

- Revision letter when the part number is a requirement of the procurement documentation.

- Designator for test points or adjustment points.

- Polarity or clocking indicators.

- U.L. designator.

The procurement documentation (artwork) is the controlling document for location and type of marking. The procurement documentation revision letter to which the board is fabricated **shall** be marked on the board if part number marking is a requirement of the procurement documentation. Marking on printed boards **shall** withstand all tests, cleaning and compatible processes to which the boards are subjected and **shall** be legible (capable of being read and understood) as defined by the requirements of this document.

The marking information on printed boards (part reference designations), **shall** be permanent and be capable of withstanding the environmental tests and cleaning procedures specified for the printed board. Marking **shall** be legible within the requirement of this document. The board **shall** be inspected at no greater magnification than 2X. When conductive inks are used they should meet the specifications of the IPC-6010 series.

This section has general requirements for all marking (including laser, labels, bar coding, etc.) and specific criteria for the following types of marking:

- Etched Markings.

- Screened or Ink Stamped Markings.

Unless otherwise specified, each individual board, each qualification board, each set of quality conformance test circuitry (as opposed to each individual coupon) is marked in accordance with the procurement documentation, with the date code and manufacturer's identification (e.g., cage code for military, logo, etc.). The marking is produced by the same process as used in producing the conductive pattern, or by use of permanent fungistatic ink or paint, or by vibrating pencil marking on a metallic area provided for marking purposes or a permanently attached label. Conductive markings, either etched copper or conductive black ink are considered as electrical elements of the board and should not reduce the electrical spacing requirements. All markings are to be compatible with materials and parts, legible for all tests, and in no case affect board performance.

Although it is acceptable to use impression stamp markings on unused portions of panels, they are not allowed on finished boards. Engraved marking or impression stamps and any mark that cuts into the laminate is handled in the same manner as a scratch.

#### 2.8 MARKING

### 2.8.1 Etched Marking

An etched marking is produced the same as the conductors on the printed board. As a result, the following criteria must be met for etched marking:

#### Target Condition - Class 1, 2, 3

- Characters are legible.

- Minimum conductor spacing requirements have also been maintained between etched symbolization and active conductors.

#### Acceptable - Class 3

- Marking defects are acceptable regardless of cause, (i.e., solder bridging, overetching, etc.) as long as characters are legible.

- Marking does not violate the minimum electrical clearance limits.

- Edges of the lines forming a character may be slightly irregular.

#### Acceptable – Class 2

- Marking defects are acceptable regardless of cause, (i.e., solder bridging, overetching, etc.) as long as characters are legible.

- Marking does not violate the minimum electrical clearance limits.

- Width of the lines forming a character may be reduced by up to 50%, providing they remain legible.

#### Acceptable – Class 1

- Marking defects are acceptable regardless of cause, (i.e., solder bridging, overetching, etc.) as long as characters are legible.

- Marking does not violate the minimum electrical clearance limits.

- Legends are irregularly formed but the general intent of the legend or marking is legible.

#### Nonconforming – Class 1, 2, 3

### 2.8.2 Screened or Ink Stamped Marking

Screened or ink stamped marking refers to any type of marking that is printed on top of the board. No cutting or etching is involved in producing this type of marking.

#### Target Condition - Class 1, 2, 3

- Characters are legible.

- Ink distribution is uniform, with no smearing or double images.

- Ink markings no closer than tangent to a land.

#### Acceptable - Class 1, 2, 3

- · Characters are legible.

- Ink may be built up outside the character line providing the character is legible.

- Portion of component clocking symbol outline may be missing, providing the required clocking is clearly defined.

- Marking ink on component hole land does not extend into the part mounting hole, or reduce minimum annular ring.

- Marking ink is allowed in plated-through holes and via holes into which no component lead is soldered unless the procurement document requires that the holes be completely solder filled.

- No encroachment of marking ink on edge board printed contacts or test points.

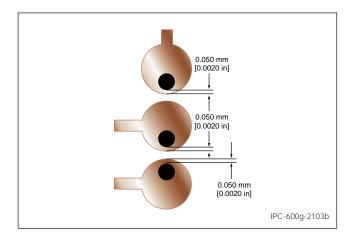

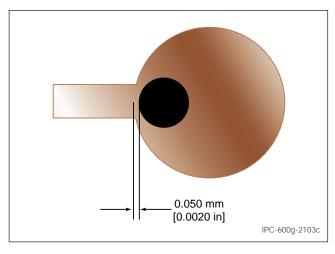

- On surface mount lands with a pitch of 1.25 mm [0.04921 in] or greater, encroachment of marking ink is on one side of land only and does not exceed 0.05 mm [0.0020 in].

- On surface mount lands with a pitch less than 1.25 mm [0.04921 in], encroachment of marking ink is on one side of land only and does not exceed 0.025 mm [0.000984 in].

#### Acceptable – Class 1

- Marking may be smeared or blurred provided it is still legible.

- Double images are legible.

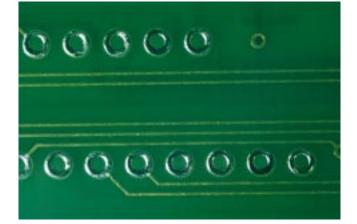

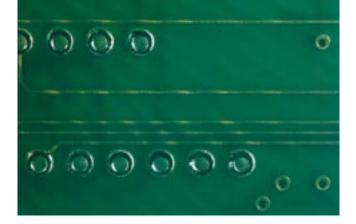

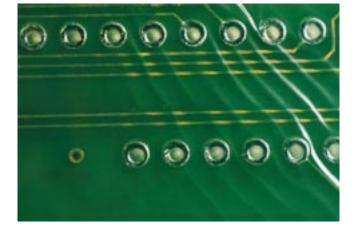

#### Nonconforming - Class 1, 2, 3

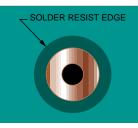

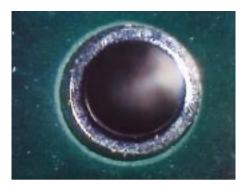

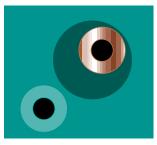

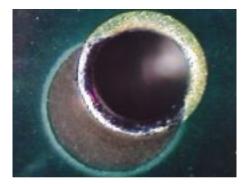

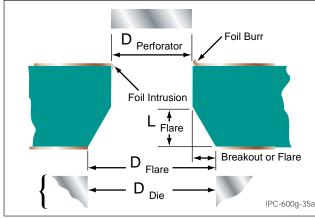

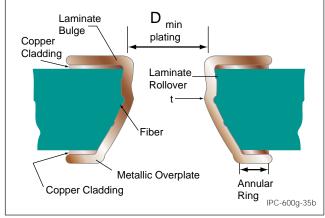

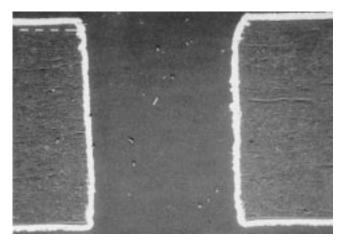

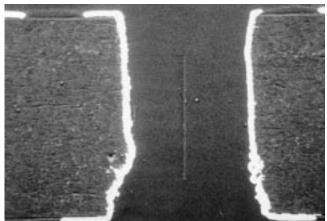

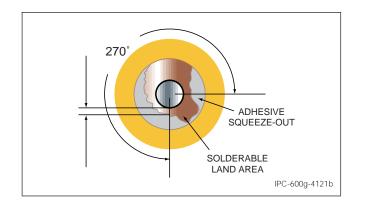

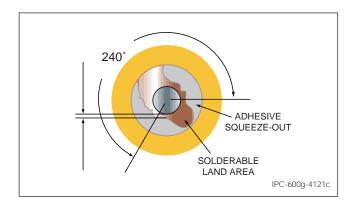

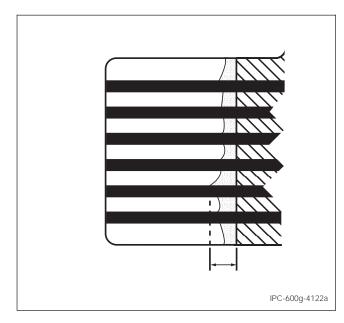

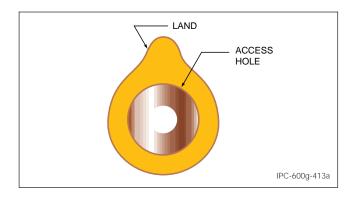

### Introduction